SANTA CLARA CONVENTION CENTER SANTA CLARA, CA

CONFERENCE:

JANUARY 31 - FEBRUARY 2, 2023

EXPO:

FEBRUARY 1-2, 2023

Register at DesignCon.com

#DesignCon

HOST SPONSOR

CORPORATE SPONSORS

**Amphenol**

PLATINUM SPONSORS

**GOLD SPONSORS**

Rambus

cādence°

ROHDE&SCHWARZ Make ideas real

SILVER SPONSORS

# **GENERAL INFORMATION**

DesignCon will take place January 31 - February 2, 2023, at the Santa Clara Convention Center in Santa Clara, CA. DesignCon welcomes Drive World and IEEE Spectrum's Emerging Chips & Markets to this year's event.

# **CONFERENCE HOURS**

Tuesday, January 31, 2023: 9:00 am – 6:00 pm Wednesday, February 1, 2023: 8:00 am – 5:15 pm Thursday, February 2, 2023: 8:00 am – 5:15 pm

# **EXHIBIT HOURS**

Wednesday, February 1, 2023: 11:00 am – 6:00 pm Thursday, February 2, 2023: 11:00 am – 6:00 pm

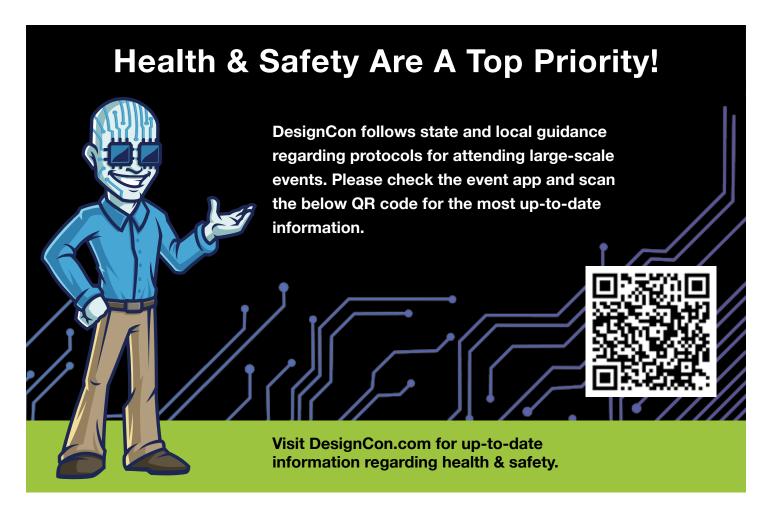

# **HEALTH & SAFETY**

Health and safety are a top priority at this event. Visit DesignCon.com for up-to-date health and safety information and check the event app for any needed communications during the event.

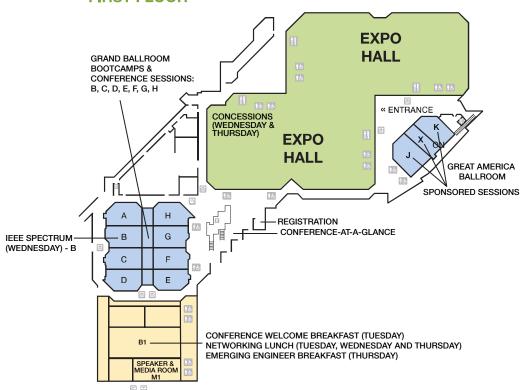

## REGISTRATION

Attendee, Speaker, Media and Exhibitor registration is located in the main lobby. Please present a photo ID when picking up your badge.

Tuesday, January 31, 2023: 8am-7pm Wednesday, February 1, 2023: 7am-6pm Thursday, February 2, 2023: 7am-6pm

## SMART EVENT

DesignCon is a Smart Event – utilize our event app and event platform for digital enhancements including networking opportunities and exhibitor profiles, featuring white papers, product information, and more. After the inperson event, all attendees, speakers, and exhibitors will still have access to our digital platform where on-demand content from DesignCon will be available at your fingertips through March 3, 2023! There's no need to register again. Your registration for DesignCon carries over to DesignCon's digital enhancements. See page 41 for more information on DesignCon's Smart Event offerings.

# **WELCOME RECEPTION**

Celebrate engineers' contributions to space exploration and enjoy complimentary cocktails, bites, games, and more at DesignCon's annual gathering on Tuesday, January 31, 6:00-8:00 pm in the Santa Clara Ballroom at the Hyatt Regency. Open to all DesignCon pass types. Badges required for entry.

Sponsored by:

# **CONCESSIONS**

Concessions are available in Exhibit Hall A in the Santa Clara Convention Center next to the Chiphead Theater.

# **CONFERENCE BREAKS**

Conference breaks will be provided for paid conference passholders, event committee members, and speakers. The breaks will be located in the conference hallways.

# CONFERENCE BREAKFAST

Complimentary breakfast is available on Tuesday, January 31 from 8:00 - 9:00 am in Mission City Ballroom B1 for all paid conference attendees, event committee members, and speakers.

# **EMERGING ENGINEER BREAKFAST**

Designed for engineers with less than 10 years of professional experience, the Emerging Engineer Breakfast runs Thursday, February 2, 8:30 - 10 am in Mission City Ballroom B1. Attendees can connect with peers looking to expand their professional reach, explore companies in electronics offering support for those emerging in their careers, and ask questions of established, highly regarded engineers and authors from the DesignCon community while enjoying a continental breakfast and raffle giveaways.

Sponsored by:

The program is subject to change without notice. Informa Markets reserves the right to alter venue, speakers, content, and/or other offerings.

# CONFERENCE NETWORKING LUNCH

Complimentary lunches are available daily from 12:30 - 2:30 pm. for paid conference passholders, event committee members, speakers, and media in Mission City Ballroom B1.

# CHIPHEAD THEATER

Check out the specialty programming in the Chiphead Theater featuring panels, training, and more right on the expo floor.

Sponsored by: Amphenol

# **DRIVE WORLD**

DesignCon welcomes Drive World back to the conference, offering an educational track for engineers looking to advance in the growing automotive electronics and intelligence industries. Drive World topics can be found under the session listings in this program. All DesignCon conference passholders have access to Drive World education.

# **IEEE SPECTRUM EMERGING CHIPS & MARKETS**

What will be the technologies driving the next great waves of innovation in semiconductors? Learn about them at this exclusive collaboration between IEEE Spectrum and DesignCon, "Emerging Chips & Markets." At this daylong track, you'll hear from the founders, executives, and researchers at the forefront of translating today's breakthroughs into tomorrow's major industries. You'll gain insights available nowhere else and get firsthand briefings about the key challenges in artificial-intelligence accelerators, wide-bandgap semiconductors, micro-LEDs, quantum computing, and more.

Visit page 10 for full details.

**IEEE Spectrum**

# PRODUCT SHOWCASE

See live, interactive demos at exhibitor booths as companies give you a first-hand look at their latest products and features. Demo schedule can be found in the main agenda and on page 48 of this show program.

# **BOOTH BAR CRAWL**

Wind down at daily meet-and-greets around the expo floor, from 5:00 - 6:00 pm, Wednesday and Thursday. Come for the conversation, stay for the bites and beverages. Please note that food will be provided around the expo floor.

Sponsored by:

Amphenol

/\nsvs

Tektronix<sup>®</sup>

Rosenberger

ROHDE&SCHWARZ

# PRESENTATION DOWNLOAD

Use the QR code below to download select speaker presentations. Note: Some presentations are available only for paid conference attendees. Login information will be emailed to paid conference attendees ahead of the event.

DesignCon 2023

Tuesday, January 31, 6–8 pm

Santa Clara Ballroom Hyatt Regency Santa Clara

Sponsored By:

Celebrate engineers' contributions to space exploration and enjoy complimentary cocktails, bites, games, and more!

Open to all DesignCon pass types. Badges required for entry.

#DesignCon

# **GENERAL INFORMATION**

# **APP**

This event utilizes a smartphone app to convey any event changes, as well as provide information, such as session details, expo maps, and hours.

Search "DesignCon 2023" in the app store to download, then sign in with the email you used to register along with your confirmation ID.

# **EVALUATIONS**

We value attendee feedback when planning the conference. Conference attendees can evaluate sessions using the below QR code.

# INFORMATION DESK

There is an information desk available outside of the main entrance to the exhibit hall and another on the expo floor in the Design News Lounge.

Stop by if you have any questions on the event or need to speak to a member of event management.

# **INTERNET ACCESS**

Wireless internet access is available throughout the building. Please use username "DesignCon" and password "amphenol" for access.

# **LOST & FOUND**

Lost and found is located at Registration.

# PUBLIC TRANSPORTATION & PARKING

Information on public transportation and the event's parking can be found on DesignCon.com's Plan Travel tab.

# **MINORS**

For safety, insurance, and security reasons, no one under the age of 18 is permitted in the expo halls or conference meeting rooms at the event. No childcare services are available onsite.

# MEDIA CENTER

Located in Mission City Ballroom M1, the Media Center is open to registered exhibitors and their representatives, as well as members of the press and analysts. You must have a media badge for access. If you would like to set up any meetings please reach out to: pr.ime@informa.com.

## SPEAKER CENTER

Located in Mission City Ballroom M1, the Speaker Center is open to registered speakers, as well as members of the DesignCon committees. You must have a speaker badge or be a current committee member for access.

This guide was created on January 10, 2023. Utilize the DesignCon 2023 app for the most up-to-date information on exhibitors, sessions, and networking.

# **EDUCATION FORUM**

**Accelerate Your Fastest Digital Designs**

Power Integrity

Signal Integrity

Simulation

USB

PCIe®

and MORE

# February 1

Visit Us in the Great America K Room

# Emerging Engineers at DesignCon

DesignCon welcomes engineers of all levels of experience – including those with less than 10 years of professional history. Mark your schedule for DesignCon's first-ever Emerging Engineer Networking Breakfast and twelve 2023 educational sessions led by engineering masters designed for this experience level.

# NEW: EMERGING ENGINEER NETWORKING BREAKFAST

Connect with peers looking to expand their professional reach, explore companies and organizations in electronics offering support for those emerging in their careers, and ask questions of established, highly regarded engineers and authors from the DesignCon community while enjoying a continental breakfast and raffle giveaways, including two All Access passes to DesignCon 2024 and gift cards.

Open to all DesignCon attendees, Thursday, February 2, 8:30-10 am.

Sponsored by:

**Amphenol**

# **EDUCATIONAL CONTENT**

# **Highlights include:**

- Hands-On PDN Impedance & Calibration Basics, presented by Keysight's Heidi Barnes, Picotest's Steve Sandler, and Northrop Grumman's Benjamin Dannan

- Quick & Easy Dielectric Constant

Measurements of Laminate Materials, taught

by Eric Bogatin, fellow with Teledyne LeCroy

and professor at University of Colorado,

Boulder

- Maintaining Manufacturing ROI for Engineering Startups

- And panels like Real-World Deployment of Al/ML in Chip & Board Applications and Test & Measurement for Automotive Standards

SCAN THE QR CODE FOR THE FULL LIST OF SESSIONS

# IEEE Spectrum Emerging Chips & Markets

What will be the technologies driving the next great waves of innovation in semiconductors? Learn about them at this exclusive collaboration between *IEEE Spectrum* and DesignCon, "Emerging Chips & Markets." At this daylong education track, you'll hear from the founders, executives, and researchers at the forefront of translating today's breakthroughs into tomorrow's major industries. You'll gain insights available nowhere else and get firsthand briefings about the key challenges in artificial-intelligence accelerators, wide-bandgap semiconductors, micro-LEDs, quantum computing, and more.

# **SESSIONS INCLUDE:**

- New Directions in Memory Technology with Tom Coughlin, President of Coughlin Associates; Debendra Das Sharma, Senior Fellow and Cogeneral Manager of Memory and I/O Technologies at Intel; and David McIntyre, Director Product Planning and Business Enablement, Device Solutions America at Samsung Semiconductor

- Hardware Approaches to Qubits with Marina Radulaski, Assistant Professor at University of California, Davis; David W. Abraham, Principal Quantum Scientist, IBM T.J. Watson Research Center; and Guy Ramon, Physics Department Chair, Santa Clara University

- Optical Fiber to the Processor with Bardia Pezeshki, CEO at Avicena; Scott Schube, Senior Director of Strategic Marketing and Business Development, Data Center Products, Intel; and Ashkan Seyedi, Silicon Photonics Product Architect, Nvidia

- Gallium Nitride vs. Silicon Carbide: Battle

of the Wide-Bandgap Semiconductors with

Umesh Mishra, Founder and CTO at Transphorm

Inc., and Robert Pilawa-Podgurski, Professor at

University of California, Berkeley

- Micro-LEDs Rise to the Challenge with Kelly Peng, CEO and Founder at Kura Technologies; Nikhil Balram, SVP and GM at Mojo Vision; and Stephen Yi, Co-Founder and CTO, Sundiode

- Revolutionary Number Formats for Machine Learning with William Dally, Chief Scientist at Nvidia, and John Gustafson, Chief Scientist at Stealth Startup

- Emerging Al Accelerator Architectures with Manouchehr Rafie, Al Accelerators Lead at Hewlett Packard Enterprise; Evgeni Gousev, Senior Director at Qualcom Technologies; Andy Hock, Vice President, Product Management at Cerebras Systems

Scan the QR Code for a full session list with descriptions.

Presented by:

**IEEE Spectrum**

# **TPC MEMBERS**

**Brice Achkir\***, Cisco Fellow/VP Eng., Cisco Systems **Joseph Aday\***, Sr. Member of Technical Staff, Lockheed Martin

Maria Agoston\*, Principal Engineer, Tektronix John Andresakis, Director of Business Development, Ohmega/Ticer Technologies

Bruce Archambeault, Retired

Pervez Aziz\*, Senior Principal Engineer, Nvidia Seungyong (Brian) Baek, SI Architect, Apple Nitin Bhagwath, Principal Technical Product Manager, Cadence

**Rula Bakleh\***, Principal SI/PI Consultant, Graphcore **Heidi Barnes\***, SI/PI Applications Engineer, Keysight Technologies

Josiah Bartlett\*, Principal Engineer in Asics and Technology Organization, Tektronix

**Wendem Beyene\***, Principal Engineer/Manager, Programmable Hardware Engineering, Intel

**Luis Boluna**, Sr. Application Engineer, Keysight Technologies

David Brunker, Technical Fellow, Molex

**Robert Carter\***, Vice President of Technology and Business Development, Oak-Mitsui Technologies

Chris Cheng\*, Distinguished Technologist, HP Enterprise David Choe, Principal Applications Engineer, Cadence Antonio Ciccomancini Scogna\*, Signal Integrity and EMC Technologist, Western Digital

**Davi Correia**, Sr. Principal Application Engineer, Cadence Design Systems

**Ben Dannan**, Technical Fellow and Staff Digital Engineer, Northrup Grumman

**O.J. Danzy**, Senior Application Engineer, Keysight Technologies

**Jan De Geest**, Senior Staff R&D Signal Integrity Engineer, Amphenol

Jay Diepenbrock, Consultant, SIRF Consultants

Vladimir Dmitriev-Zdorov, Principal Engineer, Siemens

Greg Edlund, Senior Engineer, IBM

Jason Ellison\*, Sr. Staff Signal Integrity Engineer, Amphenol

Paul Franzon, Cirrus Logic Distinguished Professor,

Director of Graduate Programs, NCSU

Sanjeev Gupta\*, Optical Network Engineer, Amazon Web Services (AWS)

Sunil Gupta, SIPI Technical Lead, Qualcomm Technologies Robert Haller\*, Sr. Principal Hardware Engineer, Extreme Networks

Gert Havermann, Signal Integrity Engineer, HARTING

Allen F. Horn III\*, Research Fellow, Rogers

Rockwell Hsu, Technical Leader, Cisco Systems

Seunghyun Hwang, Principal Engineer, Nvidia

Joungho Kim, Professor, KAIST

Namhoon Kim, Chip Package Design Architect, Google

Akhilesh Kumar, Principal R&D Engineer, Ansys

Beomtaek Lee, Sr. Principal Engineer, Intel

Mike Li\*, Fellow, Intel

Zhe Li, Hardware Engineer, Google

Cathy Liu\*, Distinguished Engineer, Broadcom

Chris Loberg\*, Marketing Manager, Tektronix

**Om Mandhana**, Staff Services AE, Cadence Design Systems

Henri Maramis, President/CEO, TrackingTheWorld Marko Marin\*, Technical Account Manager, ANSYS Jon Martens, Fellow, Anritsu

**Mehdi Mechaik\***, Sr. Signal Integrity Engineer, Amazon Lab126

Ted Mido, Principal R&D Engineer, Synopsys

Luxshare technologies is a subsidiary of Luxshare Precision, a global leader in interconnect manufacturing – servicing industries from commercial to automotive to storage and telecom.

Headquartered in Dongguan but with sales and engineering sites across the US, Europe, and Japan, Luxshare technologies can support your need for high-speed solutions around the globe. We utilize state-of-the-art engineering and manufacturing systems and equipment - from our research and development centers through our world-class manufacturing plants.

Our division employs more than 300 engineers and scientists to study and innovate in the fields of materials, interconnect design, and manufacturing processes, focused on smaller, faster, and more reliable next-generation products.

"Sometimes, the same old vendors can only provide the same tired, old solutions."

408.957.0535

820 N. McCarthy Blvd. #230, Milpitas, CA 95035

# molex

Molex helps you deliver high-power compute performance—with enhanced signal integrity and thermal management supporting 112G speeds and beyond. Visit Booth #739 for:

Live demos of next-gen IO and Enterprise 112G+ solutions

# A look at our full rack in OCP ORV-3 form factor featuring:

- 800G QSFP-DD AEC cables in a switch co-developed with Celestica

- Molex power distribution assemblies (busbar, IT gear, and BBU)

- Open Accelerator Infrastructure highlighting Mirror Mezz Mezzanine Connector

- DC-MHS system featuring NearStack PCIe, DA CEM, and other internal IO assemblies

Learn more at molex.com/designcon

# **TPC MEMBERS**

Riaz Naseer, Staff Signal Integrity Engineer, Intel Alfred P. Neves\*, Chief Technologist, Wild River Technology Istvan Novak\*, Principal Signal and Power Integrity Engineer, Samtec

Dan Oh, Vice President, Samsung

**Vishram Pandit\***, Technology Lead (Signal/Power Integrity), Intel

Jongbae Park, System SI Architect, Apple Pete Pupalaikis, VP, Technology Development, Teledyne LeCroy

**Kelvin Qiu**, Senior Signal Integrity and Power Integrity Engineer, Google

Fangyi Rao, Master Engineer, Keysight Technologies Lee Ritchey, President, Speeding Edge Gerardo Romo-Luevano\*, Sr. Staff Engineer/Manager, Qualcomm

**Steve Sandler**, Managing Director, Picotest **Venkat Satagopan\***, Sr. Staff Signal Integrity Engineer, Nvidia

**Christian Shuster**, Professor, Hamburg University of Technology (TUHH)

Yan Fen Shen, Analog Engineer, Intel

Masashi Shimanouchi, Design Engineer, Intel

Yuriy Shlepnev, President, Simberian

Ben Silva, Analog Engineer, Intel

Bert Simonovich, President, Lamsim Enterprises

Chad Smutzer, Senior Engineer, Mayo Clinic

Mike Steinberger, Consulting Software Engineer,

MathWorks

Ransom Stephens\*, Consulting Senior Scientist at BitifEye Digital Solutions and Sage at Ransom's Notes Changyi Su, Staff Design Engineer, AMD

**Suresh Subramaniam**, Principal Engineer/Architect, AMD **Madhavan Swaminathan**, John Pippin Chair Professor in Microsystems Packaging & Emag, Georgia Tech

Donald Telian, Owner/Consultant, SiGuys

Lars Thon\*, Consultant, LT Engineering

Thomas To\*. Director, AMD

**Peter Tomaszewski**, Sr. Digital Solutions Engineer, Keysight Technologies

**Ambrish Varma\***, Sr. Principal Software Engineer, Cadence Design Systems

Harald von Sosen, Principal Engineer, Siemens

Juan Wang, Senior Staff Engineer, AMD

Scott Wedge, Principal Engineer, Siemens EDA

Todd Westerhoff\*, Product Marketing Manager, Siemens

Markus Witte, Systems Engineer, Grimme

Randy Wolff, Principal Signal Integrity Engineer, Micron Technology

Hsinho Wu\*, Design Engineer, Intel

**Ken Wu**, Principal MTS, Package and SI/PI Lead, Rivos **Chris Wyland\*,** Sr. Staff Engineer, Juniper Networks

Kai Xiao, Principal Engineer, Intel

**Mobashar Yazdani\***, Strategic Semiconductor Manager, Google

Iliya Zamek, Architect, Technical Manager, HCL America Geoffrey Zhang, Distinguished Engineer and Supervisor, AMD

Pavel Zivny, Domain Expert, Tektronix

\*2023 track co-chair

# **ARE YOU A GENIUS?**

Take our DesignCon Digital Debug Challenge at Rohde & Schwarz booth #1049

Prove your GENIUS, win a prize & enter to win an RTM oscilloscope — all at DesignCon 2023

# Rambus

# HBM3, PCIe 6.0, CXL 3.0

Cutting-edge memory and interconnect interface IP for today's most challenging data center, edge, automotive and IoT applications.

# **RAMBUS TECHNICAL SESSIONS**

Wednesday, February 1, 2023 Room: Great America 1

rambus.com/designcon

# **KEYNOTES Open to All Attendees**

Aydin Aysu

Assistant Professor and Head of the Hardware Cybersecurity Research Lab (HECTOR) in the Electrical & Computer Engineering Department of North Carolina University

**Devin Billings**

Associate Director of Electrical Research and Development at Boston Dynamics

Ben Gu

Vice President Research and Development, Multiphysics System Analysis Business Unit at Cadence Design Systems

# Post-Quantum Cryptography: The Next Decade of Cryptographic Hardware Design

Tuesday, January 31, 2023 11:45am-12:30pm Elizabeth A. Hangs Theater, 2<sup>nd</sup> Floor

Existing cryptographic standard algorithms cannot move to the quantum computing era because quantum computers are proven to break them. Advances in quantum computing technology are creating concerns for such a practical break. To address this issue, we must completely change the cryptography infrastructure in the next decade and use new algorithms in secure communication and access control protocols.

# **Enabling Autonomous Robotics Through Electrical Engineering**

Wednesday, February 1, 2023 10:00-11:00am Elizabeth A. Hangs Theater, 2<sup>nd</sup> Floor

Building machines that can approximate the mobility, dexterity, and agility of people and animals is a grand challenge. Through a combination of advancements in robotic control, Al, and many forms of hardware component technology, we may be on the precipice of a proliferation of massively scalable new robotic automation opportunities. But these kinds of robots represent quite complex design challenges in electrical system design, necessitating technology that encompasses a huge range of subject matter within the electrical engineering discipline.

This keynote is preceded by the 2022 Best Paper Award presentations.

# The Intelligence to Design Intelligent Machines

Thursday, February 2, 2023 10:00-11:00am Elizabeth A. Hangs Theater, 2<sup>nd</sup> Floor

Electronics design is undergoing a revolution as semiconductors are used in more and more market applications. Each has its unique data and workload and requires customized compute and analytics architectures. Advanced semiconductors are implemented in the latest process nodes, in the most complex 3D-ICs, to achieve top performance with more operational flexibility. When the scope is expanded to the full system, complexity further exceeds the traditional siloed engineering teams and methodology. Al is showing promise for addressing the growing complexity, but not all problems are equal.

This keynote is preceded by the Engineer of the Year Award presentation.

DesignCon.com / #DesignCon

# **CONFERENCE MAP**

# **FIRST FLOOR**

# **SECOND FLOOR**

# cādence°

# **Unleash Imagination**

# Turn Great Ideas into Reality

- System design and analysis tools

- ► Silicon-proven IP

- Advanced IC packaging

- ► Photonics design automation

- ► RF to mmWave design

Visit Us in Booth 733

# DESIGNCON 2023 WHERE THE CHIP MEETS THE BOARD

Wind down at daily meet-and-greets at the front and back of the expo floor. Come for the conversation, stay for the bites and beverages.

WEDNESDAY, 5:00 - 6:00 PM

**Tektronix**<sup>®</sup>

**Amphenol**

Rosenberger

THURSDAY, 5:00 - 6:00 PM

#DesignCon

# **SESSIONS – TUESDAY, JANUARY 31**

# 8:00 AM - 9:00 AM

Welcome Breakfast

2-Day Pass, All Access Pass

**Mission City Ballroom B1**

# 9:00 AM - 4:30 PM

Boot Camp – Memory Design Fundamentals:

Next-Generation Memory Systems

All Access Pass

**Ballroom GH**

## 9:00 AM - 11:30 AM

Tutorial – Bird's-Eye Viewing 200+Gbps per Lane & Beyond with Various Signal-to-Noise Ratio Metrics

All Access Pass Ballroom F

Tutorial – Measuring PSNR/PSRR/PSMR to Meet

QSFP/OSFP High-Speed Requirements

All Access Pass Ballroom E

5 Tutorial – Quantum Computer (Superconductor Qubits) Hardware Design Guidelines

All Access Pass Ballroom D

# 11:45 AM -1 2:30 PM

Keynote – Post-Quantum Cryptography: The Next Decade of Cryptographic Hardware Design

2-Day Pass, All Access Pass,

Expo Pass Elizabeth A. Hangs Theater

## 12:30 PM - 2:30 PM

(iii) Conference Networking Lunch

2-Day Pass, All Access Pass

Mission City Ballroom B1

# 2:00 PM - 4:30 PM

Tutorial – Design & Verification for High-Speed I/Os at 10 to 112 & 224 Gbps with Jitter, Signal Integrity, & Power Optimized

All Access Pass Ballroom F

Tutorial – Machine Learning for Embedded Developers

All Access Pass Ballroom E

13 Tutorial – Stackups: The Design Within the

Design

All Access Pass Ballroom D

**(D)** Tutorial – PCB Design Techniques to Improve ESD

Robustness

All Access Pass

Ballroom C

## TRACKS AND LEGEND

### To See Speakers for Each Session - Download the DesignCon Event App

- Signal & Power Integrity for Single-Multi Die, Interposer & Packaging

- Chip I/O & Power Modeling

- 3 Integrating Photonics & Wireless in Electrical Design

- Advances in Materials & Processing for PCBs, Modules & Packages

- 6 Advanced I/O Interface Design for Memory & 2.5D/3D/SiP Integrations

- System Co-Design: Modeling, Simulation & Measurement Validation

- Optimizing High-Speed Link Design

- Measurement & Simulation Techniques for Analyzing Jitter, Noise, BER & Channel Imperfections

- High-Speed Signal Processing, Modulation, Equalization & Coding/FEC

- Power Integrity in Power Distribution Networks

- Electromagnetic Compatibility & Interference

- Applying Test & Measurement Methodology

- Modeling & Analysis of Interconnects

- Machine Learning for Microelectronics, Signaling & System Design

- Drive World Advanced Automotive

- IEEE Spectrum Emerging Chips and Markets

- **8** Best Paper Awards Finalist

- Boot Camp

- (9) Chiphead Theater Presentation

- (iii) General Event

- Special Event

- Sponsored Sessions

Conference Schedule continued on page 20.

Official

Media Sponsor:

DesignCon 2023

As official media partner of DesignCon, *Design News* serves the brightest minds looking to engineer the technology of tomorrow.

esignNews

We Inspire Innovation.

**Design News** media, educational, virtual, and live-event content explores sectors such as electronics, software and sensors, IoT, batteries, AI, AR/VR, smart manufacturing, robotics and cobots, next-generation automotive and aerospace/defense, materials, energy design implementation, and much more — to ensure that today's engineering accomplishments bring forth tomorrow's tech reality.

# **Newsletters**

Your daily fuel for trends, technology insights, and analysis for all things design engineering.

# Webinars

Keep up-to-date with our highly technical programs, with an extensive archive of content at your disposal.

designnews.com/webinars

### **Events**

Connect with other design engineering professionals in the advanced design and manufacturing community.

Subscribe to our Newsletters: designnews.com/newsletter\_signup

We'd love to hear from you. Get in touch:

# **SESSIONS – TUESDAY, JANUARY 31**

## 4:45 PM - 6:00 PM

Panel – Enabling Next Generation Co-Packaging

Solutions

2-Day Pass, All Access Pass, Expo Pass

**Ballroom D**

Panel - PCle 6.0: Challenges of Achieving 64GT/s

with PAM4 in Lossy, HVM Channels

2-Day Pass, All Access Pass, Expo Pass

Ballroom F

Panel – Real-World Deployment of Al/ML in Chip & **Board Applications**

2-Day Pass, All Access Pass, Expo Pass

**Ballroom C**

Panel – The Case of the Closing Eyes: Bridging

**FEC to Signal Integrity**

2-Day Pass, All Access Pass, Expo Pass

**Ballroom GH**

# 6:00 PM - 8:00 PM

**Welcome Reception**

Santa Clara Ballroom, Hyatt Regency Santa Clara

Sponsored by:

## TRACKS AND LEGEND

### To See Speakers for Each Session - Download the DesignCon Event App

- Signal & Power Integrity for Single-Multi Die, Interposer & Packaging

- Chip I/O & Power Modeling

- Integrating Photonics & Wireless in Electrical Design

- Advances in Materials & Processing for PCBs, Modules & Packages

- Advanced I/O Interface Design for Memory & 2.5D/3D/SiP Integrations

- System Co-Design: Modeling, Simulation & Measurement Validation

- Optimizing High-Speed Link Design

- Measurement & Simulation Techniques for Analyzing Jitter, Noise, BER & Channel Imperfections

- High-Speed Signal Processing, Modulation, Equalization & Coding/FEC

- Power Integrity in Power Distribution Networks

- Electromagnetic Compatibility & Interference

- Applying Test & Measurement Methodology

- Modeling & Analysis of Interconnects

- Machine Learning for Microelectronics, Signaling & System Design

- Drive World Advanced Automotive

- IEEE Spectrum Emerging Chips and Markets

- **(8)** Best Paper Awards Finalist

- Boot Camp

- (9) Chiphead Theater Presentation

- (iii) General Event

- Special Event

- Sponsored Sessions

Conference Schedule continued on page 22.

**IEEE Members** filed 143,349 patents last year.

Start Here > Go Anywhere! ieee.org/join

# SESSIONS - WEDNESDAY, FEBRUARY 1

# 8:00 AM - 8:45 AM

- A Novel Simulation Flow for DDR5 Systems with Clocked Receivers

- 2-Day Pass, All Access Pass

Ballroom G

- Enabling Industry's First Beyond 8.5Gbps/

- pin LPDDR5X PHY Using Rx Offset Calibration

- Scheme & Robust Training Method

- 2-Day Pass, All Access Pass

**Ballroom D**

- (2) High-Speed Loopback Applications by Utilizing a

- Differential DPDT MEMS Switch

2-Day Pass, All Access Pass

Ballroom E

- 9 Next Generation 224 Gbps-PAM4 Chip-to-Module Channel Design, Link Simulation, & Analysis

- 2-Day Pass, All Access Pass

Ballroom H

- Towards 106 GBaud: Analysis of Latest 53

- GBaud DUTs Informs the Improvements of Methodology

2-Day Pass, All Access Pass

Ballroom F

Overview of PCB Fabrication Influences on RF Performance for Millimeter-Wave Radar

2-Day Pass, All Access Pass

**Ballroom C**

New Directions in Memory Technology

2-Day Pass, All Access Pass, Expo Pass

**Ballroom B**

Technologies That Will Shape The Future Of The Data Center

2-Day Pass, All Access Pass, Expo Pass

Great America 1

# 8:00 AM - 8:40 AM

In-Situ De-Embedding

2-Day Pass, All Access Pass, Expo Pass

**Great America 2**

Advanced Testing Challenges at 32GBaud PAM4 with PCIe 6.0

2-Day Pass, All Access Pass, Expo Pass

**Great America K**

# 8:55 AM - 9:35 AM

Advanced Jittter Transfer Measurements for PLL Characterization

2-Day Pass, All Access Pass, Expo Pass

**Great America K**

# 9:00 AM - 9:45 AM

- (3) MIPI CPHY Modeling, Measurement & Correlation

- for AR/VR Devices

2-Day Pass, All Access Pass

Ballroom E

- How to Design Secured Power Delivery Network

- of Cryptographic Devices: Challenges, Evaluation

- Methods, & Solutions

2-Day Pass, All Access Pass

Ballroom D

- One-Phase Immersion Cooling Liquids

- Characterization

2-Day Pass, All Access Pass

Ballroom H

- Simulation & Analysis of Electrical/Optical Communication Links Using Free Software

- 2-Day Pass, All Access Pass

Ballroom G

## TRACKS AND LEGEND

### To See Speakers for Each Session - Download the DesignCon Event App

- Signal & Power Integrity for Single-Multi Die, Interposer & Packaging

- (2) Chip I/O & Power Modeling

- 3 Integrating Photonics & Wireless in Electrical Design

- Advances in Materials & Processing for PCBs, Modules & Packages

- 6 Advanced I/O Interface Design for Memory & 2.5D/3D/SiP Integrations

- System Co-Design: Modeling, Simulation & Measurement Validation

- Optimizing High-Speed Link Design

- Measurement & Simulation Techniques for Analyzing Jitter, Noise, BER & Channel Imperfections

- High-Speed Signal Processing, Modulation, Equalization & Coding/FEC

- Power Integrity in Power Distribution Networks

- Electromagnetic Compatibility & Interference

- Applying Test & Measurement Methodology

- Modeling & Analysis of Interconnects

- Machine Learning for Microelectronics, Signaling & System Design

- Drive World Advanced Automotive

- IEEE Spectrum Emerging Chips and Markets

- **8** Best Paper Awards Finalist

- Boot Camp

- Ohiphead Theater Presentation

- (iii) General Event

- Special Event

- Sponsored Sessions

Conference Schedule continued on page 24.

# signalintegrityjournal.com

- **EMC/EMI, Signal Integrity, and Power Integrity topics**

- In-depth, Peer-Reviewed Technical Articles

- Insights from Industry Leaders

- Product & Industry News

- Webinars & Podcasts

- White Papers

- Print editions/technical e-books

# SESSIONS - WEDNESDAY, FEBRUARY 1

# 9:00 AM - 9:45 AM

VRM Modeling & Stability Analysis for Power Integrity Engineers

2-Day Pass, All Access Pass

Ballroom F

(D) Wiring the Future of Mobility

2-Day Pass, All Access Pass

**Ballroom C**

Hardware Approaches to Qubits

2-Day Pass, All Access Pass, Expo Pass

**Ballroom B**

## 9:00 AM - 9:40 AM

Successful PCIe Interconnect Guidelines for 8, 16, and 32 GT/s

2-Day Pass, All Access Pass, Expo Pass

**Great America 2**

# 9:00 AM - 9:45 AM

Choosing The Right High-Performance Memory Solution

2-Day Pass, All Access Pass, Expo Pass

**Great America 1**

Interconnect Trends & Guidance for Automotive High-Speed Applications

2-Day Pass, All Access Pass, Expo Pass

Great America J

### 10:00 AM - 11:00 AM

Keynote – Enabling Autonomous Robotics Through Electrical Engineering

2-Day Pass, All Access Pass,

Expo Pass

Elizabeth A. Hangs Theater

# 11:10 AM - 11:50 AM

112 Gbps PAM4 Front Panel Connectivity -Real World Implementation & Correlation

2-Day Pass, All Access Pass, Expo Pass

**Great America 2**

Next Gen Development in USB4 Version 2.0

2-Day Pass, All Access Pass, Expo Pass

**Great America K**

## 11:15 AM - 12:00 PM

A New Power Integrity Requirement to Supplement Target Impedance: Quantifying PDN Impedance Flatness from Sandler NISM

2-Day Pass, All Access Pass

Ballroom G

End-to-End Security Features Protecting Mission-Critical Data for CXL Based Platforms

2-Day Pass, All Access Pass

Ballroom F

6 Best Practices for A Converged High-Speed

Channel Design for Cloud Servers in Both Air-

Cooling & Immersion-Cooling

2-Day Pass, All Access Pass

Ballroom F

Statistical BER Analysis of Concatenated FEC in

Multi-Part Links

2-Day Pass, All Access Pass

**Ballroom D**

Package & IC Aware PCB PDN Design by

Optimizing Decoupling Capacitors While Evaluating PDN Voltage Ripple Noise

3-Day Pass, All Access Pass

Ballroom H

## TRACKS AND LEGEND

### To See Speakers for Each Session - Download the DesignCon Event App

- Signal & Power Integrity for Single-Multi Die, Interposer & Packaging

- (2) Chip I/O & Power Modeling

- 3 Integrating Photonics & Wireless in Electrical Design

- Advances in Materials & Processing for PCBs, Modules & Packages

- 6 Advanced I/O Interface Design for Memory & 2.5D/3D/SiP Integrations

- System Co-Design: Modeling, Simulation & Measurement Validation

- 7 Optimizing High-Speed Link Design

- Measurement & Simulation Techniques for Analyzing Jitter, Noise, BER & Channel Imperfections

- High-Speed Signal Processing, Modulation, Equalization & Coding/FEC

- Power Integrity in Power Distribution Networks

- Electromagnetic Compatibility & Interference

- Applying Test & Measurement Methodology

- Modeling & Analysis of Interconnects

- Machine Learning for Microelectronics, Signaling & System Design

- Drive World Advanced Automotive

- IEEE Spectrum Emerging Chips and Markets

- **8** Best Paper Awards Finalist

- Boot Camp

- (9) Chiphead Theater Presentation

- General Event

- Special Event

- Sponsored Sessions

Conference Schedule continued on page 26.

**IEEE Members** have won 21 Nobel Prizes so far.

Are

Next?

Start Here ▶ Go Anywhere! ieee.org/join

# **SESSIONS – WEDNESDAY, FEBRUARY 1**

## 11:15 AM - 12:00 PM

More Relevant Than Ever: Safety & Security for Automotive Sensing Systems

2-Day Pass, All Access Pass

Ballroom C

Optical Fiber to the Processor

2-Day Pass, All Access Pass, Expo Pass

**Ballroom B**

# 11:15 AM - 12:15 PM

Panel – Deploying ML in EDA Context: Operation & Organization

2-Day Pass, All Access Pass, Expo Pass

**Chiphead Theater**

# 11:15 AM - 12:00 PM

Panel: Automotive IP Solutions For The Software-Defined Vehicle

2-Day Pass, All Access Pass, Expo Pass

**Great America 1**

OCP ORv3 Rack & Power Distribution Overview

2-Day Pass, All Access Pass, Expo Pass

Great America J

# 11:55 AM - 12:35 PM

Intuitive Simulation & Measurement Workflow for Hardware Engineers

2-Day Pass, All Access Pass, Expo Pass

**Great America K**

## 12:10 PM - 12:50 PM

Mastering Phase Noise/Jitter Measurements

2-Day Pass, All Access Pass, Expo Pass

**Great America 2**

# 12:15 PM - 1:00 PM

Data-Efficient Supervised Machine

**B** Learning Technique for Practical PCB Noise Decoupling

2-Day Pass, All Access Pass

Ballroom D

**4** Finite Element Modelling of Copper Foil Loss from

AFM Measurements

2-Day Pass, All Access Pass

**Ballroom F**

Mm-Wave Communication Over Dielectric

Waveguides: System Design & Applications

2-Day Pass, All Access Pass

**Ballroom H**

17) The IC-level Conducted Emission Measurement &

Simulation Analysis for an Automotive DRAM

2-Day Pass, All Access Pass

Ballroom G

Optimal Design & Swift Workflow for Multi-Layer Structures

2-Day Pass, All Access Pass

. . . . . . . . . . . . . . . . . . .

Designing a Configurable ECU with Python

2-Day Pass, All Access Pass

Ballroom C

Gallium Nitride vs. Silicon Carbide: Battle of the Wide-Bandgap Semiconductors

2-Day Pass, All Access Pass, Expo Pass

Ballroom B

Security IP Solutions For A World Of IoT Devices

2-Day Pass, All Access Pass, Expo Pass

**Great America 1**

### TRACKS AND LEGEND

### To See Speakers for Each Session - Download the DesignCon Event App

- Signal & Power Integrity for Single-Multi Die, Interposer & Packaging

- (2) Chip I/O & Power Modeling

- 3 Integrating Photonics & Wireless in Electrical Design

- Advances in Materials & Processing for PCBs, Modules & Packages

- 6 Advanced I/O Interface Design for Memory & 2.5D/3D/SiP Integrations

- 6 System Co-Design: Modeling, Simulation & Measurement Validation

- Optimizing High-Speed Link Design

- Measurement & Simulation Techniques for Analyzing Jitter, Noise, BER & Channel Imperfections

- High-Speed Signal Processing, Modulation, Equalization & Coding/FEC

- Power Integrity in Power Distribution Networks

- Electromagnetic Compatibility & Interference

- Applying Test & Measurement Methodology

- Modeling & Analysis of Interconnects

- Machine Learning for Microelectronics, Signaling & System Design

- Drive World Advanced Automotive

- IEEE Spectrum Emerging Chips and Markets

- **8** Best Paper Awards Finalist

- Boot Camp

- (9) Chiphead Theater Presentation

- General Event

- Special Event

- Sponsored Sessions

Conference Schedule continued on page 28.

Be sure to visit our speaker session at DesignCon 2023 and learn more about today's advanced research and studies to move your career forward.

**SPEAKER**

# PHASES OF THE IC DEVELOPMENT CYCLE

THURSDAY, FEBRUARY 2 | 11:15 AM-12:00 PM | CHIPHEAD THEATER, SANTA CLARA CONVENTION CENTER IBRAHIM DELIBALTA | Ph.D., Sr. Director of SoC Design at Intel Corporation | UCSC Extension Instructor Introduction to VLSI and ASIC Design | Spring 2023

ucsc-extension.edu

# **SESSIONS – WEDNESDAY, FEBRUARY 1**

# 12:30 PM - 1:30 PM

Panel – Advanced Technologies for Line Card Design

2-Day Pass, All Access Pass, Expo Pass

**Chiphead Theater**

# 12:30 PM - 2:30 PM

Conference Networking Lunch

2-Day Pass, All Access Pass

**Mission City Ballroom B1**

# 1:45 PM - 2:30 PM

Maintaining Manufacturing ROI for Engineering Startups

2-Day Pass, All Access Pass, Expo Pass

**Chiphead Theater**

# 2:00 PM - 2:45 PM

A Novel Approach to 224 Gb/s Reference Receiver

Design Using Raised Cosine Response for Noise Mitigation

2-Day Pass, All Access Pass

Ballroom G

A Novel Crosstalk Reduction Technique for DDR5

Server Application

2-Day Pass, All Access Pass

**Ballroom E**

7 An Innovative CPU Pin-Field Routing for Signal

Integrity Optimization

2-Day Pass, All Access Pass

Ballroom D

# 2:00 PM - 2:45 PM

MIMO Crosstalk Cancelation Technique in Serial Electrical Links

2-Day Pass, All Access Pass

Ballroom H

Measurement Bandwidth & Its Impact on

Accuracy

2-Day Pass, All Access Pass

Ballroom F

O 4K eDP Vehicular Display Micro-Coax Cable Designs

2-Day Pass, All Access Pass

Ballroom C

Micro-LEDs Rise to the Challenge

2-Day Pass, All Access Pass, Expo Pass

**Ballroom B**

## 2:00 PM - 2:40 PM

Far-End Crosstalk In High-Speed PCB Channels

2-Day Pass, All Access Pass, Expo Pass

Great America 2

# 2:00 PM - 2:45 PM

Accelerating Data Interconnects With PCI Express 6.0 Interface IP

2-Day Pass, All Access Pass, Expo Pass

**Great America 1**

224G Connector Solution

2-Day Pass, All Access Pass, Expo Pass

**Great America J**

## TRACKS AND LEGEND

# To See Speakers for Each Session – Download the DesignCon Event App

- Signal & Power Integrity for Single-Multi Die, Interposer & Packaging

- Chip I/O & Power Modeling

- 3 Integrating Photonics & Wireless in Electrical Design

- Advances in Materials & Processing for PCBs, Modules & Packages

- 6 Advanced I/O Interface Design for Memory & 2.5D/3D/SiP Integrations

- System Co-Design: Modeling, Simulation & Measurement Validation

- Optimizing High-Speed Link Design

- Measurement & Simulation Techniques for Analyzing Jitter, Noise, BER & Channel Imperfections

- High-Speed Signal Processing, Modulation, Equalization & Coding/FEC

- Power Integrity in Power Distribution Networks

- Electromagnetic Compatibility & Interference

- Applying Test & Measurement Methodology

- Modeling & Analysis of Interconnects

- Machine Learning for Microelectronics, Signaling & System Design

- Drive World Advanced Automotive

- IEEE Spectrum Emerging Chips and Markets

- **8** Best Paper Awards Finalist

- Boot Camp

- (9) Chiphead Theater Presentation

- (iii) General Event

- Special Event

- Sponsored Sessions

Conference Schedule continued on page 30.

# **SESSIONS – WEDNESDAY, FEBRUARY 1**

## 2:40 PM - 3:20 PM

Physical Layer Validation Challenges of Characterizing 100/200 Gbps/lane Designs

2-Day Pass, All Access Pass, Expo Pass

**Great America K**

# 2:45 PM - 3:00 PM

Accurate SI Analysis for PCIe Gen5 Signaling with

PCB & Connector Merged Structure up to 50GHz

2-Day Pass, All Access Pass, Expo Pass

**Chiphead Theater**

# 3:00 PM - 3:40 PM

Dielectric Permittivity Extraction For Inhomogeneous Dielectric Layers Based On Delta-L & Extended Unterminated Line (EUL) Measurements

2-Day Pass, All Access Pass, Expo Pass

**Great America 2**

## 3:00 PM - 3:45 PM

- Comprehensive Statistical Analysis of SERDES

- Links Considering DFE Error Propagation

- 2-Day Pass, All Access Pass

- ML-Based AMOP Framework for On-chip Test Sequence Thermal Optimization

2-Day Pass, All Access Pass

Ballroom H

**Ballroom G**

- 6 PCIe 6.0 (PAM4) Signal Integrity Challenges in

- Immersion-Cooling Datacenters

2-Day Pass, All Access Pass

Ballroom D

# 3:00 PM - 3:45 PM

- PCle Gen5, Signal Integrity Implementation Issues

- & Solutions

2-Day Pass, All Access Pass

Ballroom E

- The Influence of EM Field Solver Numerical

- Solution Space on Measurement Correlation to 50GHz & Beyond

2-Day Pass, All Access Pass

**Ballroom F**

Pushing the Boundaries of Automotive Connectivity

2-Day Pass, All Access Pass

Ballroom C

Revolutionary Number Formats for Machine Learning

2-Day Pass, All Access Pass, Expo Pass

**Ballroom B**

## 3:00 PM - 3:45 PM

CXL Advances Data Center Performance With Memory Tiering Architecture

2-Day Pass, All Access Pass, Expo Pass

**Great America 1**

# 3:15 PM - 4:00 PM

- Panel Will Al Ever Replace Engineers?

- 2-Day Pass, All Access Pass, Expo Pass

**Chiphead Theater**

### TRACKS AND LEGEND

# To See Speakers for Each Session - Download the DesignCon Event App

- Signal & Power Integrity for Single-Multi Die, Interposer & Packaging

- (2) Chip I/O & Power Modeling

- 3 Integrating Photonics & Wireless in Electrical Design

- Advances in Materials & Processing for PCBs, Modules & Packages

- 6 Advanced I/O Interface Design for Memory & 2.5D/3D/SiP Integrations

- 6 System Co-Design: Modeling, Simulation & Measurement Validation

- Optimizing High-Speed Link Design

- Measurement & Simulation Techniques for Analyzing Jitter, Noise, BER & Channel Imperfections

- High-Speed Signal Processing, Modulation, Equalization & Coding/FEC

- Power Integrity in Power Distribution Networks

- Electromagnetic Compatibility & Interference

- Applying Test & Measurement Methodology

- Modeling & Analysis of Interconnects

- Machine Learning for Microelectronics, Signaling & System Design

- Drive World Advanced Automotive

- IEEE Spectrum Emerging Chips and Markets

- **8** Best Paper Awards Finalist

- Boot Camp

- (9) Chiphead Theater Presentation

- (iii) General Event

- Special Event

- Sponsored Sessions

Conference Schedule continued on page 32.

# Explore the Cutting Edge

Engineers turn to *Tech Briefs* for new design ideas and solutions to their toughest manufacturing challenges. We report the latest technology breakthroughs from NASA and other leading R&D sources worldwide.

Keep pace with the latest breakthroughs in:

- Electronics

- Test & Measurement

- Computing

- Bio-medical

- Mechatronics

- Software

- Data Acquisition

- Cameras & Imaging

Join over 160,000 design engineers & managers throughout OEM industries, who rely on *Tech Briefs* to stay on the cutting edge, and gain a competitive advantage.

You may also qualify to receive

Aerospace & Defense Technology, from the publishers of Tech Briefs.

Start your subscription today at:

www.techbriefs.com/SUBSCRIBE/TB/DESIGNCON23

For information on marketing to this audience of highly qualified BUYERS, visit **www.saemediagroup.com** or contact Joe Pramberger, publisher, at 917-286-3758; joe.pramberger@saemediagroup.com.

# **SESSIONS – WEDNESDAY, FEBRUARY 1**

## 3:30 PM - 4:10 PM

IBIS/IBIS-AMI for SerDes and Memory Applications

2-Day Pass, All Access Pass, Expo Pass

Great America K

# 4:00 PM - 4:40 PM

Improve Power Integrity With Pre-Layout Decoupling Solutions

2-Day Pass, All Access Pass, Expo Pass

**Great America 2**

# 4:00 PM - 5:15 PM

Panel – Compute Express Link (CXL) 3.0: Enabling

New Usage Models in Composable Disaggregated Infrastructure

2-Day Pass, All Access Pass, Expo Pass

Ballroom D

6 Panel – Enabling Next Generation Architectures: 224 Gbps Electrical Interfaces

2-Day Pass, All Access Pass, Expo Pass

Ballroom G

Panel – What Users Need from Power Integrity Simulators

2-Day Pass, All Access Pass, Expo Pass

**Ballroom F**

Panel – Revolutionizing In-Vehicle PHY Channel Characterization (>10Gbps): Is Simulation the Solution?

2-Day Pass, All Access Pass, Expo Pass

Ballroom C

Emerging Al Accelerator Architectures

2-Day Pass, All Access Pass, Expo Pass

Ballroom B

## 4:15 PM - 5:00 PM

Micro-coax Cable Transfer Performance of

High-speed Differential Signals

2-Day Pass, All Access Pass, Expo Pass Chiphead Theater

# 4:20 PM - 5:00 PM

Advanced Power Integrity Simulation & Measurement Methods

2-Day Pass, All Access Pass, Expo Pass

Great America K

# 5:00 PM - 6:00 PM

Booth Bar Crawl

2-Day Pass, All Access Pass, Expo Pass

**Expo Hall**

Sponsored by:

# **Tektronix**<sup>®</sup>

**Amphenol**

Rosenberger

## TRACKS AND LEGEND

### To See Speakers for Each Session - Download the DesignCon Event App

- Signal & Power Integrity for Single-Multi Die, Interposer & Packaging

- (2) Chip I/O & Power Modeling

- 3 Integrating Photonics & Wireless in Electrical Design

- Advances in Materials & Processing for PCBs, Modules & Packages

- 6 Advanced I/O Interface Design for Memory & 2.5D/3D/SiP Integrations

- System Co-Design: Modeling, Simulation & Measurement Validation

- Optimizing High-Speed Link Design

- Measurement & Simulation Techniques for Analyzing Jitter, Noise, BER & Channel Imperfections

- High-Speed Signal Processing, Modulation, Equalization & Coding/FEC

- Power Integrity in Power Distribution Networks

- Electromagnetic Compatibility & Interference

- Applying Test & Measurement Methodology

- Modeling & Analysis of Interconnects

- Machine Learning for Microelectronics, Signaling & System Design

- Drive World Advanced Automotive

- IEEE Spectrum Emerging Chips and Markets

- **8** Best Paper Awards Finalist

- Boot Camp

- (9) Chiphead Theater Presentation

- (iii) General Event

- Special Event

- Sponsored Sessions

Conference Schedule continued on page 34.

# SUBSCRIBE NOW TO: Electronic Design.

# STAY ON TOP OF THE LATEST TECHNOLOGY LAUNCHES AND TRENDS TAKING PLACE IN THE ELECTRONICS INDUSTRY.

Subscribe to the magazine—in print or digital format as well as targeted newsletters for a variety of electronics areas including analog, power, test and measurement, and more. www.electronicdesign.com/subscribe

# **SESSIONS – THURSDAY, FEBRUARY 2**

# 8:00 AM - 8:45 AM

- Analytical Models for FEC Symbol Error Distribution

- of DFE Propagation with Precoding and EoBD

2-Day Pass, All Access Pass

Ball

- Cff at affirm Dair Olaman Oakla

- Fifect of Intra-Pair Skew on Copper Cable

Assembly Link Performance

- 2-Day Pass, All Access Pass Ballroom E

- (1) Extremely Fast Dynamic Link Equalization for PCle

- Based on Imitation Learning

- 2-Day Pass, All Access Pass

Ballroom D

- Impact Evaluation of Fiber-Weave Effect Induced

- 5 Delay Uncertainty in DDR Data Links on DDR5 & Towards DDR6

- 2-Day Pass, All Access Pass

Ballroom F

- Noise in Traffic: Signal Emulation for

- Automotive Apps

- 2-Day Pass, All Access Pass

Ballroom H

- Centralized Storage for Next Generation Vehicles: New Standards & Future Roadmaps

- 2-Day Pass, All Access Pass

Ballroom C

- How to Measure Jitter Induced by Power Distribution Network (PDN) Noise

- 2-Day Pass, All Access Pass, Expo Pass

**Great America K**

Addressing Package/PCB Thermal Challenges by Extending Your Power Integrity Analysis Methodology

2-Day Pass, All Access Pass, Expo Pass

**Great America J**

# 8:30 AM - 10:00 AM

Emerging Engineer Breakfast

2-Day Pass, All Access Pass,

Expo Pass Mission City Ballroom B1

# 9:00 AM - 9:45 AM

- 3D Connection Artifacts in PDN

- Measurements

- 2-Day Pass, All Access Pass

- A Case Study of Soft Information & Decoding

- Concatenated Codes for Optical Applications

2-Day Pass, All Access Pass

Ballroom D

- **5** Cost Optimized PCB Design for DDR5

- 3 2-Day Pass, All Access Pass

- Managing Differential Via Crosstalk & Ground Via

- Placement for 40+ Gbps Signaling

- 2-Day Pass, All Access Pass Ballroom F

- System Design Challenges with 5G & mmwWave Integration

- 2-Day Pass, All Access Pass

Ballroom H

Ballroom G

**Ballroom E**

- Beyond 10Gbps Automotive Ethernet: Is Optical Connectivity the Solution?

- 2-Day Pass, All Access Pass

Ballroom C

- USB4® Version 2.0 Transmitter (Tx) & Receiver (Rx) Electrical Compliance Test Update

- 2-Day Pass, All Access Pass, Expo Pass

- **Great America K**

- PowerTree-based PDN Analysis, Correlation & Signoff for AR Systems

- 2-Day Pass, All Access Pass, Expo Pass

**Great America J**

## TRACKS AND LEGEND

### To See Speakers for Each Session - Download the DesignCon Event App

- Signal & Power Integrity for Single-Multi Die, Interposer & Packaging

- (2) Chip I/O & Power Modeling

- 3 Integrating Photonics & Wireless in Electrical Design

- Advances in Materials & Processing for PCBs, Modules & Packages

- 6 Advanced I/O Interface Design for Memory & 2.5D/3D/SiP Integrations

- System Co-Design: Modeling, Simulation & Measurement Validation

- Optimizing High-Speed Link Design

- Measurement & Simulation Techniques for Analyzing Jitter, Noise, BER & Channel Imperfections

- High-Speed Signal Processing, Modulation, Equalization & Coding/FEC

- Power Integrity in Power Distribution Networks

- Electromagnetic Compatibility & Interference

- Applying Test & Measurement Methodology

- Modeling & Analysis of Interconnects

- Machine Learning for Microelectronics, Signaling & System Design

- Drive World Advanced Automotive

- IEEE Spectrum Emerging Chips and Markets

- **8** Best Paper Awards Finalist

- Boot Camp

- (9) Chiphead Theater Presentation

- General Event

- Special Event

- Sponsored Sessions

Conference Schedule continued on page 36.

THE WORLD'S SOURCE FOR EMBEDDED **ELECTRONIC ENGINEERING INFORMATION**

**Engineers rely on Circuit Cellar!**

From embedded systems design to embedded programming, wireless communications, robotics, sensor systems, IoT technology, analog techniques, programming tips, and so much more.

Circuit Cellar magazine delivers the most in-demand engineering-related information, ideas, and solutions.

MINI

circuit cenar

MCU VENDORS REV UP NEW SECURITY SOLUTIONS

# **SESSIONS – THURSDAY, FEBRUARY 2**

# 10:00 AM - 11:00 AM

Keynote – The Intelligence to Design Intelligent

Machines

2-Day Pass, All Access Pass, Expo Pass

Elizabeth A. Hangs Theater

# 11:15 AM - 12:00 PM

Accuracy & Challenges of PAM4 Jitter & Noise

Measurements for >100Gbps Serial Links

2-Day Pass, All Access Pass

Ballroom F

7 Design of a SI/PI Optimized PCIe 6 Platform to

Enable PCle 7

2-Day Pass, All Access Pass

Ballroom D

(3) Cascaded vs End-to-End Multi-Pin Interconnect

Simulation Models

2-Day Pass, All Access Pass

Ballroom H

Data-Driven PAM4 SerDes Modeling & Generative Adversarial Network

2-Day Pass, All Access Pass

Ballroom G

**Material Series of Multiple Series of Multiple Series**1. \*\*The Compatible Behavior Model of Multiple Series\*\*

1. \*\*The Compatible Behavior Model of Multiple Behavior Model of Multipl

Woltage Regulator Module for End-to-End Power Integrity Simulation

2-Day Pass, All Access Pass

Ballroom F

Feasibility of End-to-End Ethernet for Sensor & Display Connectivity in Automotive Applications

2-Day Pass, All Access Pass

Ballroom C

# 11:15 AM - 12:00 PM

How To Debug USB4® PHY-Logic & Sideband Links

2-Day Pass, All Access Pass, Expo Pass

**Great America K**

When Chips Become 3D Systems – The Challenges of Designing Multi-Chiplet Packages

2-Day Pass, All Access Pass, Expo Pass

**Great America J**

Phases of the IC Development Cycle

2-Day Pass, All Access Pass, Expo Pass

**Chiphead Theater**

# 12:15 PM - 1:00 PM

Evaluating 224G SI Performance of Discrete

DC Blocking Capacitors on Optical Modules & Systems

2-Day Pass, All Access Pass

Ballroom E

**COM Based IBIS-AMI Correlation Including Actual System & Circuit Behaviors for 106/112Gb/s**

2-Day Pass, All Access Pass

Ballroom D

Designing the Best Reference Transmitter for

Serdes Testing: AWG vs BER

2-Day Pass, All Access Pass

Ballroom F

NextGen Copper Foils for High-Speed Digital & Radio Frequency Applications

2-Day Pass, All Access Pass

Ballroom G

Scalable Capacitor ESL Curve Fitting for Various Stack-ups

2-Day Pass, All Access Pass

Ballroom H

### TRACKS AND LEGEND

### To See Speakers for Each Session - Download the DesignCon Event App

- Signal & Power Integrity for Single-Multi Die, Interposer & Packaging

- (2) Chip I/O & Power Modeling

- 3 Integrating Photonics & Wireless in Electrical Design

- Advances in Materials & Processing for PCBs, Modules & Packages

- 6 Advanced I/O Interface Design for Memory & 2.5D/3D/SiP Integrations

- System Co-Design: Modeling, Simulation & Measurement Validation

- Optimizing High-Speed Link Design

- Measurement & Simulation Techniques for Analyzing Jitter, Noise, BER & Channel Imperfections

- High-Speed Signal Processing, Modulation, Equalization & Coding/FEC

- Power Integrity in Power Distribution Networks

- (ii) Electromagnetic Compatibility & Interference

- Applying Test & Measurement Methodology

- Modeling & Analysis of Interconnects

- Machine Learning for Microelectronics, Signaling & System Design

- Drive World Advanced Automotive

- IEEE Spectrum Emerging Chips and Markets

- **8** Best Paper Awards Finalist

- Boot Camp

- (9) Chiphead Theater Presentation

- (iii) General Event

- Special Event

- Sponsored Sessions

Conference Schedule continued on page 38.

#

## THE NAVIGATOR FOR ENTERPRISE SOLUTIONS

#### **SESSIONS – THURSDAY, FEBRUARY 2**

#### 12:15 PM - 1:00 PM

Multi-Sensor Annotation & Calibration is the Key Unlocking ADAS Applications

2-Day Pass, All Access Pass

Ballroom C

Chipheads: Hands-On PDN Impedance & Calibration Basics

2-Day Pass, All Access Pass, Expo Pass

**Chiphead Theater**

Cross-layer Analysis & Debug of PCI Express® Power Management & Link Training

2-Day Pass, All Access Pass, Expo Pass

Great America K

Encore Presentation: Optimal Design & Swift Workflow for Multi-Layer Structures

2-Day Pass, All Access Pass, Expo Pass

**Great America J**

#### 12:30 PM - 2:30 PM

Conference Networking Lunch

2-Day Pass, All Access Pass

**Mission City Ballroom B1**

#### 1:15 PM - 2:00 PM

Quick & Easy Dielectric Constant Measurements of Laminate Materials

2-Day Pass, All Access Pass, Expo Pass

**Chiphead Theater**

#### 2:00 PM - 2:45 PM

3D EM Full Wave Analysis & Optimization

for Source Synchronous Interconnect in Heterogeneous Integration Architecture

2-Day Pass, All Access Pass

Ballroom G

Distributed-Physical-Based Transmission-

**Line Model of PCle5 Connector for SI Fast Diagnosis**

2-Day Pass, All Access Pass

**Ballroom D**

High Speed System Architecture Design of DCN

Core Switch

2-Day Pass, All Access Pass

Ballroom E

12 IP/PHY & Testing are Critical for USB4

Version 2.0

2-Day Pass, All Access Pass

Ballroom H

Rigorous Correlation Methodology for PCIe Gen5

& Gen6 DSP Based IBIS-AMI Models

2-Day Pass, All Access Pass

Ballroom F

(D) The Billion Dollar Mistake

2-Day Pass, All Access Pass

Ballroom C

Understanding & Implementing PCI Express® 6.0 Receiver Test Requirements

2-Day Pass, All Access Pass, Expo Pass

Great America K

Envisioning the Future of Power Integrity Through the Eyes of Experience

2-Day Pass, All Access Pass, Expo Pass

**Great America J**

#### TRACKS AND LEGEND

#### To See Speakers for Each Session - Download the DesignCon Event App

- Signal & Power Integrity for Single-Multi Die, Interposer & Packaging

- (2) Chip I/O & Power Modeling

- 3 Integrating Photonics & Wireless in Electrical Design

- Advances in Materials & Processing for PCBs, Modules & Packages

- 6 Advanced I/O Interface Design for Memory & 2.5D/3D/SiP Integrations

- System Co-Design: Modeling, Simulation & Measurement Validation

- 7 Optimizing High-Speed Link Design

- Measurement & Simulation Techniques for Analyzing Jitter, Noise, BER & Channel Imperfections

- High-Speed Signal Processing, Modulation, Equalization & Coding/FEC

- Power Integrity in Power Distribution Networks

- Electromagnetic Compatibility & Interference

- Applying Test & Measurement Methodology

- Modeling & Analysis of Interconnects

- Machine Learning for Microelectronics, Signaling & System Design

- Drive World Advanced Automotive

- IEEE Spectrum Emerging Chips and Markets

- **8** Best Paper Awards Finalist

- Boot Camp

- (9) Chiphead Theater Presentation

- General Event

- Special Event

- Sponsored Sessions

Conference Schedule continued on page 40

### **Get Charged Up!**

Become part of the fast growing advanced battery and electric & hybrid vehicles technology community.

May 23-25, 2023 | Stuttgart, Germany

September 12-14, 2023 | Novi, Michigan

October 4-6, 2023 | Greater Noida

For more information please visit:

TheBatteryShow.com

#### **SESSIONS – THURSDAY, FEBRUARY 2**

#### 2:15 PM - 3:00 PM

Backplanes, Speed Gains & Architectural Autonomy: Evolution of Copper Interconnects

2-Day Pass, All Access Pass, Expo Pass

**Chiphead Theater**

#### 3:00 PM - 3:45 PM

A Simple TDR Technique to Measure the Dielectric

Constant of Any Layer in a Multi-Layer Printed

Circuit Board

2-Day Pass, All Access Pass

Ballroom E

An EMI Reduction Modeling Approach of PCB & Shielding Enclosures Using the Lua-based Automation

2-Day Pass, All Access Pass

Ballroom H

- IBIS-AMI Modeling & Simulation for PAM3

- Signaling in USB4 Gen4 Systems

2-Day Pass, All Access Pass

**Ballroom G**

Learning Beyond Low-Quality Data Distribution:

An Application to Optimal Decap Placement

2-Day Pass, All Access Pass

Ballroom F

#### 3:00 PM - 3:45 PM

Measurement-Based Bias Voltage, Temperature, & Light Intensity Effect on the Through-silicon Vias (TSVs)

2-Day Pass, All Access Pass

Ballroom D

(D) Supply & Demand Trends in Automotive ICs

2-Day Pass, All Access Pass

**Ballroom C**

PCI Express® 6.0 Transmitter Electrical Test Overview

2-Day Pass, All Access Pass, Expo Pass

**Great America K**

Optimizing 3D-IC Power Delivery with Pre-Route System-Level Simulation

2-Day Pass, All Access Pass, Expo Pass

**Great America J**

#### 3:15 PM - 4:00 PM

Limits of High speed Connector & Cable Technology, Part 2

2-Day Pass, All Access Pass, Expo Pass

**Chiphead Theater**

#### TRACKS AND LEGEND

#### To See Speakers for Each Session - Download the DesignCon Event App

- Signal & Power Integrity for Single-Multi Die, Interposer & Packaging

- Chip I/O & Power Modeling

- 3 Integrating Photonics & Wireless in Electrical Design

- Advances in Materials & Processing for PCBs, Modules & Packages

- 6 Advanced I/O Interface Design for Memory & 2.5D/3D/SiP Integrations

- System Co-Design: Modeling, Simulation & Measurement Validation

- Optimizing High-Speed Link Design

- Measurement & Simulation Techniques for Analyzing Jitter, Noise, BER & Channel Imperfections

- High-Speed Signal Processing, Modulation, Equalization & Coding/FEC

- Power Integrity in Power Distribution Networks

- Electromagnetic Compatibility & Interference

- Applying Test & Measurement Methodology

- Modeling & Analysis of Interconnects

- Machine Learning for Microelectronics, Signaling & System Design

- Drive World Advanced Automotive

- IEEE Spectrum Emerging Chips and Markets

- **8** Best Paper Awards Finalist

- Boot Camp

- (9) Chiphead Theater Presentation

- (iii) General Event

- Special Event

- Sponsored Sessions

Conference Schedule continued on page 42.

#### DesignCon 2023 is a Smart Event

Your access to DesignCon's education and expo doesn't end this week!

Throughout the week on-site, utilize our event app and event platform for digital enhancements including networking opportunities and exhibitor profiles, featuring white papers, product information, and more. After the in-person event, all attendees, speakers, and exhibitors will still have access to our digital platform where on-demand content from DesignCon will be available at your fingertips through March 3, 2023!

**No need to register again** – Your registration for this week's in-person event carries over to DesignCon's digital enhancements.

Scan the below for more information on DesignCon's Smart Event offerings.

#### **SESSIONS – THURSDAY, FEBRUARY 2**

#### 4:00 PM - 5:15 PM

Panel – FEC for Next Generation 800G/1.6T

Ethernet Systems

2-Day Pass, All Access Pass, Expo Pass

Ballroom G

Panel – PCI Express Specification: A High-

Bandwidth, Low-Latency Interface for the Compute Continuum

2-Day Pass, All Access Pass, Expo Pass

**Ballroom F**

3 Panel – Photonics Future: Vision, Challenges, and the Path to Infinity & Beyond!

2-Day Pass, All Access Pass, Expo Pass

**Ballroom D**

#### 4:00 PM - 5:15 PM

Panel – Test on Wheels: Test & Measurement for Automotive Standards

2-Day Pass, All Access Pass, Expo Pass

Ballroom C

A Simple Method For De-embedding Fixtures Using S-parameter Measurements

2-Day Pass, All Access Pass, Expo Pass

**Great America K**

PCle Rising: The Journey to 64Gb/s and 128Gb/s

2-Day Pass, All Access Pass, Expo Pass

**Great America J**

#### 4:15 PM - 5:00 PM

Panel - Overcoming Career Challenges for Millenials

2-Day Pass, All Access Pass, Expo Pass

**Chiphead Theater**

#### 5:00 PM - 6:00 PM

Booth Bar Crawl

2-Day Pass, All Access Pass, Expo Pass

Expo Hall

Sponsored by:

Rosenberger

Tektronix<sup>®</sup>

**/**Insys

ROHDE&SCHWARZ

#### TRACKS AND LEGEND

#### To See Speakers for Each Session - Download the DesignCon Event App

- Signal & Power Integrity for Single-Multi Die, Interposer & Packaging

- Chip I/O & Power Modeling

- 3 Integrating Photonics & Wireless in Electrical Design

- Advances in Materials & Processing for PCBs, Modules & Packages

- 6 Advanced I/O Interface Design for Memory & 2.5D/3D/SiP Integrations

- System Co-Design: Modeling, Simulation & Measurement Validation

- Optimizing High-Speed Link Design

- Measurement & Simulation Techniques for Analyzing Jitter, Noise, BER & Channel Imperfections

- High-Speed Signal Processing, Modulation, Equalization & Coding/FEC

- Power Integrity in Power Distribution Networks

- Electromagnetic Compatibility & Interference

- Applying Test & Measurement Methodology

- Modeling & Analysis of Interconnects

- Machine Learning for Microelectronics, Signaling & System Design

- Drive World Advanced Automotive

- IEEE Spectrum Emerging Chips and Markets

- **8** Best Paper Awards Finalist

- Boot Camp

- (9) Chiphead Theater Presentation

- (iii) General Event

- Special Event

- Sponsored Sessions

## Check Out The DesignCon Mobile App

Search "DesignCon 2023" in your app store to download the app, sign in with the email you used to registered along with your confirmation ID.

- → Find exhibitors

- → Connect with other attendees

- → Create your event schedule

- → Navigate the expo floor

#DesignCon

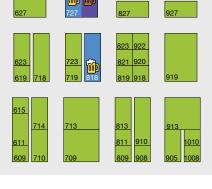

#### **EXHIBITOR LIST**

| Company                                                     | Booth     |

|-------------------------------------------------------------|-----------|

| Company                                                     | Dootii    |

| 219 Design                                                  | 1010      |

| Accurate Circuit Engineering                                | 1054      |

| ACES Electronics                                            | 713       |

| Advanced Test Equipment Re<br>AGC Multi Material America, I | ntals 859 |

| AGC Multi Material America, I                               | nc. 954   |

| Altair                                                      | 526       |

| Amphenol                                                    | 833       |

| Anritsu Company                                             | MR1462    |

| Ansys<br>APCT                                               | 748       |

| APCT                                                        | 522       |

| Applied Brain Research, Inc.                                | 1045      |

| Argosy Research Inc.                                        | 811       |

| Astera Labs, Inc.                                           | 854       |

| ATTEND Technology Inc.                                      | 1341      |

| Avishtech                                                   | 913       |

| Bellwether Electronic Corp                                  | 710       |

| BizLink Technology, Inc.                                    | 1249      |

| Cadence Design Systems                                      | 733       |

| Carlisle Interconnect Technological                         | gies 818  |

| Circuit Foil Luxembourg                                     | 610       |

| ColorChip Technology                                        | 523       |

| Co-Tech Development Corp.                                   | 319       |

| CR Technology, Inc.                                         | 858       |

| Cvilux USA                                                  | 323       |

| CWB Electronics, Inc.                                       | 424       |

| Cyth Systems, Inc.                                          | 809       |

| Dassault Systèmes Simulia Co                                | orp. 527  |

| DOOSAN Corporation Electro                                  | -         |

| Materials BG <sup>'</sup>                                   | 618       |

| DuPont Electronic Solutions                                 | 608       |

| DVT Solutions, LLC                                          | 619       |

| Elantas PDG, Inc.                                           | 1359      |

| Electro Rent Corporation                                    | 1239      |

| Elite Material Co. Ltd. (EMC)                               | 955       |

| Ellisys                                                     | 755       |

| EMA Design Automation Inc.                                  | 714       |

| EMCoS LLC                                                   | 422       |

| Epson America, Inc.                                         | 512       |

| ept USA                                                     | 960       |

| eTopus Technology Inc                                       | 1257      |

| evissaP                                                     | 922       |

| Flexible Circuit Technologies I                             |           |

| Flex Logix Technologies, Inc.                               | 609       |

| FOCI                                                        | 759       |

| Foresight Finishing                                         | 1343      |

| Fotofab, LLC                                                | 1155      |

| GetWireless                                                 | 412       |

| Granite River Labs                                          | 857       |

| Hirose Electric USA                                         | 949       |

| Huber+Suhner, Inc.                                          | 1243      |

| Company                                             | Booth |

|-----------------------------------------------------|-------|

| Company                                             | DOULL |

| Huwin                                               | 959   |

| Hyperlabs                                           | 1055  |

| Imagineering Inc.                                   | 419   |

| In Compliance                                       | 821   |

| Informa Markets                                     | 100x  |

| Insulated Wire Inc                                  | 1444  |

| I-PEX                                               | 1342  |

| Ironwood Electronics                                | 515   |

| Isola Group                                         | 627   |

| ITEQ Corporation                                    | 415   |

| IWIN Co., Ltd.                                      | 1441  |

| JAE Electronics, Inc.                               | 1139  |

| JPC Connectivity                                    | 1158  |

| JS Electronics                                      | 1357  |

| Junkosha Inc.                                       | 1059  |

| Kandou Bus S.A.                                     | 418   |

| Keysight Technologies                               | 1039  |

| KGS America Inc.                                    | 813   |

| Kingmate Electronic Co., Ltd.                       | 1154  |

| Langer EMV-Technik GmbH                             | 1442  |

| Leeno Industrial Inc.                               | 1349  |

| Lotes Co., Ltd                                      | 910   |

| Luxshare-ICT                                        | 839   |

| Malico Inc.                                         | 1440  |

| MathWorks                                           | 927   |

| Menlo Micro                                         | 908   |

| Molex                                               | 739   |

| Monogoto                                            | 719   |

| Mouser Electronics                                  | 827   |

| MPI Corporation                                     | 1438  |

| MultiLane                                           | 749   |

| Neoconix                                            | 423   |

| Oak-Mitsui Technologies LLC                         | 855   |

| Ohmega Technologies                                 | 519   |

| OpenSystems Media                                   | 511   |

| PacketMicro, Inc.                                   | 1255  |

|                                                     |       |

| PalPilot International Panasonic Industrial Devices | 409   |

| Sales Company of America                            | 611   |

| PFC Flexible Circuits                               | 1345  |

|                                                     | 1354  |

| Pico Technology                                     |       |

| Plastronics                                         | 315   |

| Polar Instruments Rigol Technologies USA            | 622   |

|                                                     | 1149  |

| RoBAT Ltd                                           | 723   |

| Rogers Corporation                                  | 614   |

| Rohde & Schwarz USA, Inc.                           | 1049  |

| Rosenberger North America                           | 1047  |

| S2C Limited                                         | 327   |

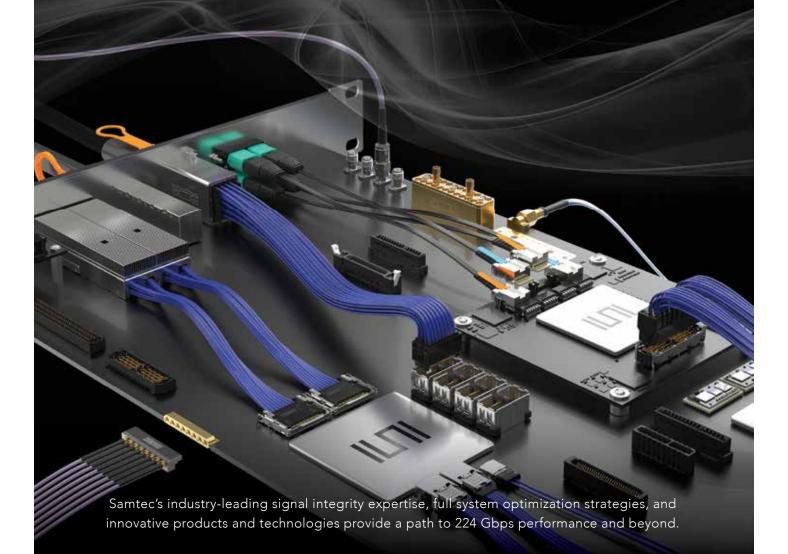

| Samtec USA                                          | 939   |

| Company                          | Booth |

|----------------------------------|-------|

| Sanmina                          | 718   |

| <b>SENKO Advanced Components</b> | 1058  |

| Shengyi Technology               | 426   |

| Siemens Digital Industries       |       |

| Software                         | 849   |

| Siglent Technologies Co., Ltd.   | 1254  |

| Signal Microwave                 | 623   |