### Amphenol COMMUNICATIONS SOLUTIONS

# Curious about how we solve complex electronic design challenges?

Visit the newest technology demonstrations for connectors and cables at Booth #833

# DesignCon 2022 is a Smart Event

Your access to DesignCon's education and expo doesn't end in Santa Clara!

After the in-person event, all attendees, speakers, and exhibitors will have access to our digital platform for recordings of select content from DesignCon, new education exclusively available online, networking opportunities, and exhibitor profiles, featuring white papers, product information, and more.

No need to register again – Your registration for the in-person event carries over to DesignCon's online offerings.

Scan the below for more information on DesignCon's online Smart Event offerings.

**#DesignCon**

# THE TECHNICAL RENAISSANCE IS SILICON-TO-SILICON SOLUTIONS

Samtec's Silicon-to-Silicon solutions exceed today's connectivity demands reaching 112 Gbps with a path of 224 Gbps and beyond.

# **WELCOME RECEPTION**

# TUESDAY, APRIL 5 | 6-8 PM

TERRA COURTYARD, HYATT REGENCY SANTA CLARA

Sponsored By:

# Enjoy complimentary cocktails, bites, games and more!

Open to all DesignCon, Drive World, and Embedded IoT World attendees, exhibitors, speakers, media, and committee members. (Badges required for entry.)

(

**#DesignCon**

### **TPC MEMBERS**

We would like to thank the volunteers who served on the Technical Program Committee (TPC) for DesignCon 2022. Their contributions as reviewers of the abstracts and papers have made it possible for us to maintain the DesignCon standard of excellence and deliver an outstanding program again this year.

**Brice Achkir**\*, Distinguished Eng./Sr. Eng. Director, Cisco Systems

Joseph Aday\*, Sr. Member of Technical Staff, Lockheed Martin Maria Agoston\*, Principal Engineer, Tektronix Ravinder Ajmani, Technologist, Electronic Design

Engineering, Western Digital John Andresakis, Technical Marketing Leader, DuPont

Yianni Antoniades, Senior Electrical Engineer, Winchester Interconnect

Bruce Archambeault, Retired

Pervez Aziz\*, Senior Principal Engineer, Nvidia Seungyong (Brian) Baek, SI Architect, Apple Nitin Bhagwath, Principal Technical Product Manager, Cadence

**Rula Bakleh**\*, Principal SI/PI Engineer, Graphcore **Heidi Barnes**\*, SI/PI Applications Engineer, Keysight Technologies

**Josiah Bartlett\***, Principal Engineer in Asics and Technology Organization, Tektronix

Dale Becker, Distinguished Engineer, IBM

Wendem Beyene\*, Principal Engineer/Manager, Programmable Hardware Engineering, Intel Luis Boluna, Sr. Application Engineer, Keysight Technologies

David Brunker, Technical Fellow, Molex

Robert Carter\*, Vice President of Technology and Business Development, Oak-Mitsui Technologies Chris Cheng\*, Distinguished Technologist, HP Enterprise David Choe, Principal Applications Engineer, Cadence Antonio Ciccomancini Scogna\*, Signal Integrity and EMC Technologist, Western Digital Davi Correia, Sr. Principal Application Engineer, Cadence Design Systems

**O.J. Danzy**, Senior Application Engineer, Keysight Technologies Jan De Geest, Senior Staff R&D Signal Integrity Engineer, Amphenol Jay Diepenbrock, Consultant, SIRF Consultants Vladimir Dmitriev-Zdorov, Principal Engineer, Siemens Greg Edlund, Senior Engineer, IBM Jason Ellison\*, Sr. Staff Signal Integrity Engineer, Amphenol Paul Franzon, Cirrus Logic Distinguished Professor, Director of Graduate Programs, NCSU Sanjeev Gupta\*, R&D Manager, Intel Sunil Gupta, SIPI Technical Lead, Qualcomm Technologies Robert Haller\*, Sr. Principal Hardware Engineer, Extreme Networks Gert Havermann, Signal Integrity Engineer, HARTING Allen F. Horn III\*, Research Fellow, Rogers Rockwell Hsu, Technical Leader, Cisco Systems Seunghyun Hwang, Principal Engineer, Nvidia Joungho Kim, Professor, KAIST Namhoon Kim, Chip Package Design Architect, Google Beomtaek Lee, Sr. Principal Engineer, Intel Mike Li\*, Fellow, Intel Zhe Li, Hardware Engineer, Google Cathy Liu\*, Distinguished Engineer, Broadcom Chris Loberg\*, Marketing Manager, Tektronix Om Mandhana, Staff Services AE, Cadence Design Systems Henri Maramis, President/CEO, TrackingTheWorld Marko Marin\*, Technical Account Manager, ANSYS Jon Martens, Fellow, Anritsu Mehdi Mechaik\*, Sr. Signal Integrity Engineer, Amazon Lab126 Ted Mido, Principal R&D Engineer, Synopsys

### **TPC MEMBERS**

Martin Miller, Chief Scientist, Teledyne LeCroy Akshay Mohan, EM Technology Lead, Amazon Lab126 Jose Moreira\*, Senior Staff Engineer, Advantest Zhen Mu\*, Product Engineering Architect, Cadence Design Systems Riaz Naseer, Staff Signal Integrity Engineer, Intel Alfred P. Neves\*, Chief Technologist, Wild River Technology Istvan Novak\*, Principal Signal and Power Integrity Engineer, Samtec Dan Oh, Vice President, Samsung Vishram Pandit\*, Technology Lead (Signal/Power Integrity), Intel Jongbae Park, System SI Architect, Apple Pete Pupalaikis, VP, Technology Development, Teledyne LeCroy Kelvin Qiu, Senior Signal Integrity and Power Integrity Engineer, Google Fangyi Rao, Master Engineer, Keysight Technologies Lee Ritchey, President, Speeding Edge Gerardo Romo-Luevano\*, Sr. Staff Engineer/Manager, Qualcomm Steve Sandler, Managing Director, Picotest Venkat Satagopan\*, Sr. Staff Signal Integrity Engineer, Nvidia Yan Fen Shen, Analog Engineer, Intel Masashi Shimanouchi, Design Engineer, Intel Yuriy Shlepnev, President, Simberian Ben Silva, Analog Engineer, Intel Bert Simonovich, President, Lamsim Enterprises Chad Smutzer, Senior Engineer, Mayo Clinic Mike Steinberger, Consulting Software Engineer, **MathWorks**

Ransom Stephens\*, Consulting Senior Scientist at BitifEve Digital Solutions and Sage at Ransom's Notes Changyi Su, Staff Design Engineer, AMD Suresh Subramaniam, Principal Engineer/Architect, AMD Madhavan Swaminathan, John Pippin Chair Professor in Microsystems Packaging & Emag, Georgia Tech Donald Telian, Owner/Consultant, SiGuys Lars Thon\*, Consultant, LT Engineering Thomas To\*, Director, AMD Peter Tomaszewski, Sr Field Applications Engineer, Tektronix Ambrish Varma\*, Sr. Principal Software Engineer, Cadence Design Systems Harald von Sosen, Principal Engineer, Siemens Juan Wang, Senior Staff Engineer, AMD Scott Wedge, Principal Engineer, Siemens EDA Todd Westerhoff\*, Product Marketing Manager, Siemens Markus Witte, Systems Engineer, Grimme Randy Wolff, Principal Signal Integrity Engineer, Micron Technology Hsinho Wu\*, Design Engineer, Intel Ken Wu, Principal MTS, Package and SI/PI Lead, Rivos Chris Wyland\*, Sr. Staff Engineer, Juniper Networks Kai Xiao, Principal Engineer, Intel Mobashar Yazdani\*, Strategic Semiconductor Manager, Google Iliya Zamek, Architect, Technical Manager, HCL America Geoffrey Zhang, Distinguished Engineer and Supervisor, AMD Pavel Zivny, Domain Expert, Tektronix

\*2022 track co-chair

# Accelerate Your Fastest Digital Designs EDUCATION FORUM

PCIe6 Power Integrity Signal Integrity Next-Gen Type-C Next-Gen Memory Forward Error Correction

# **April 7th** Visit Us in Mission City Ballroom B4

Anritsu | Since 1895

# Advancing Innovation from Inspiration to Validation

# Panel: The Case of the Closing Eyes: PAM4 is Here!

April 5 4:45pm - 6pm Ballroom GH

# + Anritsu Test Talks

April 6 9am - 5:15pm Mission City Ballroom B5

### A full day of education and live demos

- + FEC Uncorrectable Error Analysis

- + TDR Measurements with VNAs

- + PCle<sup>®</sup> 6.0 & Beyond

- + PAM4 BER & Jitter Tolerance Test

- + DisplayPort<sup>™</sup> 2.0, Thunderbolt<sup>™</sup> 3,

USB4<sup>™</sup> Receiver Test

- + AND MORE!

Learn about our presentations, demos & more: info.goanritsu.com/designcon2022

Meet our Solution Experts

Booth #1014

Advancing beyond

### **GENERAL INFORMATION**

#### **LOCATION & DATES**

DesignCon will take place April 5-7, 2022, at the Santa Clara Convention Center in Santa Clara, CA. DesignCon welcomes Drive World and Embedded IoT World to this year's event.

#### **CONFERENCE HOURS**

Tuesday, April 5, 2022: 9:00 am – 6:00 pm Wednesday, April 6, 2022: 8:00 am – 5:15 pm Thursday, April 7, 2022: 8:00 am – 5:15 pm

#### **EXHIBIT HOURS**

Wednesday, April 6, 2022: 11:00 am – 6:00 pm Thursday, April 7, 2022: 11:00 am – 6:00 pm

#### **HEALTH & SAFETY**

Health and safety are a top priority at this event. Visit DesignCon.com for up-to-date health and safety information and check the event app for any needed communications during the event.

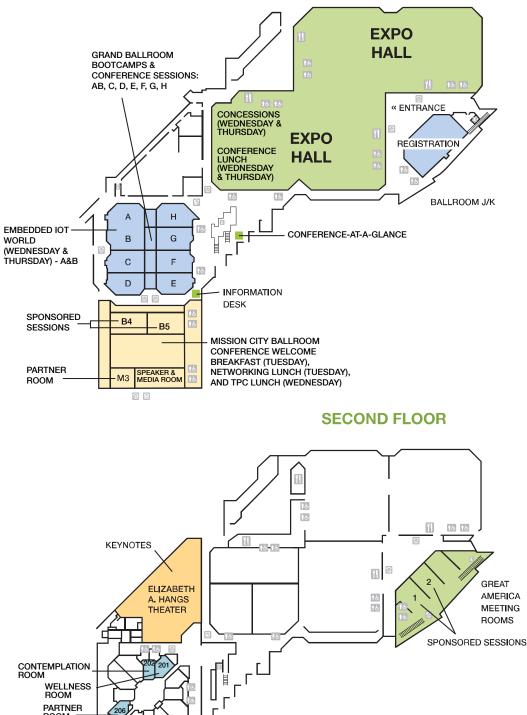

#### REGISTRATION

Attendee, Speaker, Media and Exhibitor registration is located in Great America Ballroom J and X on the first floor of the convention center. Please present a photo ID when picking up your badge.

Tuesday, April 5: 7:00 am – 5:00 pm Wednesday, April 6: 7:00 am – 6:00 pm Thursday, April 7: 7:00 am – 6:00 pm

#### **SMART EVENT**

DesignCon is a smart event - a hybrid experience that extends the value of DesignCon beyond the three days in Santa Clara. As a pass holder you have access to our digital platform, Swapcard, where you can make connections with exhibitors, speakers and attendees; view product information; and watch exclusive content. Visit DesignCon.com for more details.

#### WELCOME RECEPTION

Enjoy complimentary cocktails, bites, games, and more at DesignCon's annual gathering on Tuesday, April 5, 6:00-8:00 pm on the Terra Courtyard at the Hyatt Regency. This year's open-to-all pass types reception is themed as a Spring Break for engineers. Badges required for entry. Sponsored by:

#### **CONCESSIONS**

Concessions are available in Exhibit Hall A in the Santa Clara Convention Center next to the Chiphead Theater.

#### **CONFERENCE BREAKS**

Conference breaks will be provided for paid conference passholders, event committee members and speakers. The breaks will be located in the conference hallways at the following times:

Tuesday, April 5: Morning Break: 11:30 – 11:45 am Afternoon Break: 4:30 – 4:45 pm

Wednesday, April 6 & Thursday, April 7: Morning Breaks: 8:45 – 9:00 am, 9:45 – 10 am Afternoon Breaks: 2:45 – 3:00 pm, 3:45 – 4:00 pm

#### **CONFERENCE BREAKFAST**

Complimentary breakfast is available on Tuesday, April 5 from 8:00 - 9:00 am in Mission City Ballroom B1 for all paid conference attendees, event committee members and speakers.

The program is subject to change without notice. Informa Markets reserves the right to alter venue, speakers, content, and/or other offerings.

# Embedded IoT World

Taking place at **DESIGNCON® 2022**

# **EMBEDDED SYSTEMS TO CREATE** SAFE, RELIABLE & SECURE IOT

Take your embedded systems knowledge to the next level whilst at DesignCon at Embedded IoT World in Ballroom B, April 6 - 7. Curated by engineers, for engineers, learn directly from the technical specialists bringing end-to-end IoT to life and take back tangible ideas to propel your projects forward.

### **LEVEL-UP YOUR EXPERTISE AT SESSIONS LIKE:**

#### APP STARTUP COMPILER OPTIMIZATIONS & TECHNOLOGIES FOR EMBEDDED SYSTEMS

ADITYA KUMAR Senior Software Engineer / Compiler Engineer Snap Inc.

### WEDNESDAY APRIL 6, 2022

TOWARDS IOT DEVICE INTEGRATION IN SMART HOMES (LUNCH INSIDER SESSION/WORKSHOP)

ALESSANDRO BASSANO Principal Security Research Scientist Technology Innovation Institute

#### LESSONS LEARNED FROM BUILDING A CONNECTED ARTIFICIAL NOSE USING TINYML

BENJAMIN CABE Principal Program Manager, Azure IoT Microsoft

# THURSDAY APRIL 7, 2022

#### SMOKE & MIRRORS: COMMUNICATION IN THE IOT WORLD

ROBERT HAFERNIK Principal Key Expert Engineering Siemens

#### IT'S JUST A VULNERABLE COMPUTER: PROTECTING AUTONOMOUS SYSTEMS

JULIA DOWNES Principal Embedded Operating Systems Engineer Defence Science & Technology Laboratory (GOV UK)

#### WANT TO PUT YOUR LEARNING INTO ACTION? WHY NOT COME AND MEET OUR AWE-INSPIRING EXHIBITORS...

#EIOTWORLD

# **GENERAL INFORMATION**

#### **CONFERENCE NETWORKING LUNCH**

Complimentary lunches are available daily for paid conference attendees, event committee members, and speakers.

Tuesday, April 5: Mission City Ballroom B1 Wednesday, April 6 & Thursday, April 7: Expo Floor

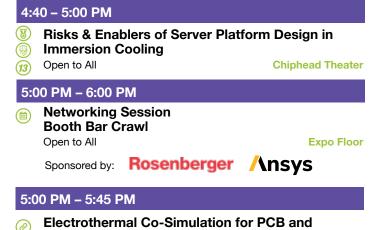

#### **CHIPHEAD THEATER**

Check out the specialty programming in the Chiphead Theater featuring panels, training, and more right on the expo floor.

Sponsored by: Amphenol

#### **DRIVE WORLD**

DesignCon welcomes Drive World back to the conference, offering an educational track for engineers looking to advance in the growing automotive electronics and intelligence industries. Drive World topics can be found under the session listings in this program. All DesignCon conference passholders have access to Drive World education.

#### **EMBEDDED IoT WORLD**

Embedded IoT World, in partnership with DesignCon, provides a curated program for engineers, architects, and developers using embedded technologies to bring endto-end IoT solutions to life. Free to explore for all pass holders, you'll be able to access technical sessions to build your expertise and learn how to tackle your biggest implementation challenges. You're also invited to discover new technologies and meet with key solution providers in silicon, chip design, semiconductors, processors, connectivity, and more on the expo floor.

#### Embedded IoT World

#### **PRODUCT SHOWCASE**

See live, interactive demos at exhibitor booths as companies give you a first-hand look at their latest products and features. Demo schedule can be found in the main agenda.

#### **BOOTH BAR CRAWL**

Wind down at daily meet-and-greets around the expo floor, from 5:00 - 6:00 pm, Wednesday and Thursday. Come for the conversation, stay for the bites and beverages. Please note that food will be provided around the expo floor.

Sponsored by: Amphenol

CARLISLE

Rosenberger Ansys

#### PRESENTATION DOWNLOAD

Use the QR code below to download select speaker presentations. Note: Some presentations are available only for paid conference attendees. Login information will be emailed to paid conference attendees ahead of the event.

### **5-DAY COURSES**

- Earn Free IEEE credits

- Access to entire course archive

- Interactive chat session to tackle and solve technical issues

- Download additional learning materials

#### **REGISTER TODAY**

www.designnews.com/ continuing-education-center

# **DesignNews**

# 2022

The Digi-Key Continuing Education Center, presented by Design News, is a well-established, highly technical program with an extensive archive of content at your disposal.

Our highest-attended courses include: Raspberry PI, IoT Device Prototyping, Embedded Software Development Design Techniques, and many more.

### SPEAKERS:

## FRED EADY

Principal Engineer Georgia Branch of Ongoing Systems

### **JACOB BENINGO**

Embedded Software Consultant Beningo Embedded Group

#### **DON WILCHER**

Electrical Engineer, Technical Author & Researcher MaDon Research

### **GENERAL INFORMATION**

#### **LOST & FOUND**

Lost and found is located at Registration.

#### **PUBLIC TRANSPORTATION & PARKING**

Information on public transportation and the event's parking rates can be found on DesignCon.com's Plan Travel tab.

#### **MINORS**

For safety, insurance, and security reasons, no one under the age of 18 is permitted in the expo halls or conference meeting rooms at the event. No childcare services are available onsite.

#### MEDIA CENTER

Located in Mission City Ballroom M1 and M2, the Media Center is open to registered exhibitors and their representatives, as well as members of the press and analysts. You must have a media badge for access. If you would like to set up any meetings please reach out to: pr.ime@informa.com.

#### **SPEAKER CENTER**

Located in Mission City Ballroom M1 and M2, the Speaker Center is open to registered speakers, as well as members of the DesignCon committees. You must have a speaker badge or be a current committee member for access.

#### APP

This event utilizes a smartphone app to convey any event changes, as well as provide information, such as session details, expo maps, and hours.

Search "Informa Markets Events" in the app store to download, then log-in using the same email address you used to register for this event and select "DesignCon" from the event choices.

#### **EVALUATIONS**

We value attendee feedback when planning the conference. Conference attendees can evaluate sessions using the below QR code.

#### **INFORMATION DESK**

There is an information desk available in the Conference Hallway near the entrance to the Mission City Ballroom and another on the expo floor in the Design News Lounge. Stop by if you have any questions on the event or need to speak to a member of event management.

#### **INTERNET ACCESS**

Wireless internet access is available throughout the building. Please use username "DesignCon" and password "amphenol" for access.

# INSTANT INSIGHTS MEETS IN-DEPTH INFORMATION

Attend the full-day seminar series Wednesday, April 6<sup>th</sup> 1 8am-5pm Great America Meeting Room 2

INTRODUCING THE R&S®RTO6 OSCILLOSCOPE SERIES

ROHDE&SCHWARZ

# **Rambus** SerDes & Memory Interfaces

A comprehensive suite of SerDes and memory interface IP for today's most challenging data center, edge, automotive and IoT applications.

# **RAMBUS TECHNICAL SESSIONS**

Wednesday, April 6 Room: Great America 1

rambus.com/designcon

# **KEYNOTES Open to All Attendees**

John Bowers Fred Kavli Chair of Nanotechnology University of California Santa Barbara

Laurence Moroney Artificial Intelligence Lead Google

José Morey Consultant for NASA, IBM, Hyperloop Transportation, Liberty BioSecurity Health and Technology Progress Enabled: The Convergence of Photonic & Electronic ICs

Tuesday, April 5, 2022 12:00 pm-12:45 pm Elizabeth A. Hangs Theater

Advancements are happening that will drive the future direction of the data center, and put silicon photonics at the heart of this push. The current convergence of progress in silicon photonics and electronics means that co-packaged silicon photonics and electronics enable the continued progress of both fields and propel further innovation in both.

# The Realities of AI & Machine Learning: Cut Through the Hype & Move to Production

Wednesday, April 6, 2022 10:00-11:00 am Elizabeth A. Hangs Theater

We've all heard about the potential of AI and machine learning. Learn from a developer's perspective how machine learning can give a new programming paradigm that makes AI possible and enables problem solving that was previously infeasible.

This keynote is preceded by the Best Paper Award presentation.

#### **Space Tech: Present & Future**

Thursday, April 7, 2022 10:00-11:00 am Elizabeth A. Hangs Theater

The rapid commercialization of space has gone beyond creating the first quadrillion dollar industry and developed the first truly limitless economy. In this talk we will explore the technology and innovations that are bringing about a truly consequential change for our civilization.

This keynote is preceded by the Engineer of the Year Award presentation.

Luxshare-Tech proudly presents our latest technology in interconnects and cable assemblies at DesignCon 2022. Our recent product release includes up to 112G PAM4 DACs and Active Copper Cables (ACC) using Luxshare's own OptamaxTM bulk cable and QSFP112G DR4 modules. Please stop by our booth at DesignCon (booth #839) to experience our exciting live demos.

LUXSHARE-Tech' s 112G PAM4 direct attached passive copper cable assemblies enable next generation high-speed data communication. By combining eight channels, operating at speeds up to 112 Gbps per lane into one affordable high-density media data interface (MDI) and providing aggregate data throughput in excess of 800 Gbps. Leveraging LUXSHARE' s own proprietary OptamaxTM ultra low loss twin-axial raw cable, and carefully designed MSA compliant paddle card and cage technology, LUXSHARE-Tech' s 112G PAM4 DACs over industry leading signal integrity and thermal performance for server, storage, and switch applications.

For more information

Our internal high speed interconnect solution supports next generation servers using our OmniEdgeTM family of products. In addition we offer MCIO, GEN-Z cable, and SlimSAS cable assemblies and board connectors supports up to PCIE 6.0; Low profile SlimSAS cable assemblies and board connectors supports up to SAS4.0, with anti-skew interface.

Luxshare' s copper loopbacks are offered in QSFP-DD / QSFP28/ SFP28 form factors. Our loopbacks support adjustable power consumption optimizing switch verification to be more cost-effective.

Luxshare-Tech's optics supports 10G to 400G data rate, for the applications over 1,000 meters connectivity length.

# **CONFERENCE MAP**

#### **FIRST FLOOR**

THE BO

CONTEMPLATION ROOM WELLNESS ROOM

PARTNER ROOM -

#### 8:00 AM – 9:00 AM

- **Networking Session** ( **Conference Welcome Breakfast** All Access Pass **Mission City Ballroom B1** 9:00 AM - 4:30 PM

- Boot Camp AI & Deep Learning for SI/PI (14)

- All Access Pass  $(\mathbf{1})$

#### 9:00 AM - 11:30 AM

- Tutorial Design & Verification for High-Speed (8) I/Os at 10 to 112 & 224Gbps with Jitter, Signal Integrity & Power Optimized All Access Pass **Ballroom EF**

- Tutorial PAM6 Signaling: A Potential Candidate (9) at 224Gbps  $\overline{\mathbf{7}}$

All Access Pass

**Ballroom AB**

**Ballroom GH**

#### 12:00 PM - 12:45 PM

- Keynote Progress Enabled: The Convergence of **Photonic & Electronic ICs**

- Open to All **Elizabeth A. Hangs Theater**

#### 12:30 PM - 2:30 PM

- **Networking Session Conference Networking Lunch** All Access Pass **Mission City Ballroom B1** 2:00 PM - 4:30 PM Tutorial – OSFP/QSFP-DD 112G PAM4 Channel for (13) **800G System Applications**  $\overline{7}$ All Access Pass **Ballroom AB** Tutorial – Over the Air Testing of 5G AiP Modules 3 in High-volume Manufacturing All Access Pass **Ballroom D** Tutorial – The Real World of Power Integrity & (10) Signal Integrity Working Together All Access Pass **Ballroom EF** 4:45 PM - 6:00 PM

- Panel AMI Models & the Seven-year Itch

- Open to All  $\overline{7}$

#### TRACKS AND LEGEND

To See Speakers for Each Session – Download the DesignCon Event App

- () Signal & Power Integrity for Single-Multi Die, Interposer & Packaging

- (2) Chip I/O & Power Modeling

- Integrating Photonics & Wireless in Electrical Design

- Advances in Materials & Processing for (4) PCBs, Modules & Packages

- Advanced I/O Interface Design for Memory & 2.5D/3D/SiP Integrations

- System Co-Design: Modeling, Simulation & Measurement Validation 6

- (7) Optimizing High-Speed Link Design

- Measurement & Simulation Techniques for Analyzing Jitter, Noise & BER

- High-Speed Signal Processing, Equalization & Coding/FEC

- Power Integrity in Power Distribution (10) Networks

- 1 Electromagnetic Compatibility & Interference

- Applying Test & Measurement Methodology

- Modeling & Analysis of Interconnects

- Machine Learning for Microelectronics, (14) Signaling & System Design

Drive World – Advanced Automotive

**Ballroom AB**

- Embedded IoT World

- (8) Best Paper Awards Finalist

- Boot Camp

- Chiphead Theater Presentation

- (iii) General Event

- ↔ Special Event

- Ø Sponsored Sessions

#### 4:45 PM – 6:00 PM

- Panel CXL & PCIe Technologies: The Next (5) **Generation of Interconnects** (7 Open to All **Ballroom EF**

- Panel The Case of the Closing Eyes:

- PAM-N, What Can be Tested?

- Open to All

- D Panel Bringing AI to the Edge: Hardware & Software Enables Autonomous AI Ecosystem on the Edge Open to All

**Ballroom C**

**Ballroom GH**

#### 6:00 PM - 8:00 PM

Sponsored by:

- **Networking Session (**

- Welcome Reception Æ

Open to All

Terra Courtyard at the Hyatt Regency

#### TRACKS AND LEGEND

- () Signal & Power Integrity for Single-Multi Die, Interposer & Packaging

- (2) Chip I/O & Power Modeling

- Integrating Photonics & Wireless in Electrical Design

- Advances in Materials & Processing for PCBs, Modules & Packages (4)

- Advanced I/O Interface Design for (5) Memory & 2.5D/3D/SiP Integrations

- 6 System Co-Design: Modeling, Simulation & Measurement Validation

- (7) Optimizing High-Speed Link Design

- Measurement & Simulation Techniques for (8) Analyzing Jitter, Noise & BER

- High-Speed Signal Processing, **(9)** Equalization & Coding/FEC

- Power Integrity in Power Distribution 10 Networks

- 1 Electromagnetic Compatibility & Interference

- Applying Test & Measurement Methodology

- Modeling & Analysis of Interconnects

- (14) Machine Learning for Microelectronics, Signaling & System Design

- Drive World Advanced Automotive

- Embedded IoT World

- (8) Best Paper Awards Finalist

- 🛞 Boot Camp

- Chiphead Theater Presentation

- General Event

- ↔ Special Event

- Ø Sponsored Sessions

# **Tektronix**<sup>®</sup>

# ACCELERATE THE SPEED OF TEST

- Meet our experts

- Experience our hands-on demos

- See what's new

# BOOTH #827

#EngineeringTheFuture

| 8:0          | 00 AM – 8:45 AM                                                                                                                      |                             |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| 8<br>6       | A New Challenge for Neuromorphic<br>Systems: From Off-chip Interconne<br>Interconnects                                               | ects to On-chip             |

| ( <b>1</b> ) | All Access Pass, 2-Day Pass                                                                                                          | Ballroom D                  |

| 8<br>5<br>1  | A Processing-In-memory on High-<br>Memory (PIM-HBM): Impact of Inte<br>Channels on System Performance<br>All Access Pass, 2-Day Pass | erconnect                   |

|              |                                                                                                                                      |                             |

| 10           | A Step-by-step Guide to a Novel La<br>PDN Co-simulation Methodology<br>All Access Pass, 2-Day Pass                                   | ab Correlated<br>Ballroom F |

| 1            | Onchip ESD Protection Structure M<br>Methodology                                                                                     | -                           |

|              | All Access Pass, 2-Day Pass                                                                                                          | Ballroom E                  |

| 13<br>12     | Validation of Achieving 200Gbps Si<br>Electrical Lane Over 1 Meter of Pas<br>Copper Cable                                            |                             |

|              | All Access Pass, 2-Day Pass                                                                                                          | Ballroom H                  |

| D            | Challenges & Solutions in Physical<br>for Automotive Wired Communicat                                                                |                             |

|              | All Access Pass, 2-Day Pass                                                                                                          | Ballroom C                  |

#### All Access Pass, 2-Day Pass

#### 8:00 AM - 8:40 AM

| Ø       | In-Situ De-embedding<br>Open to All                                                         | Great America Meeting Room 2                               |

|---------|---------------------------------------------------------------------------------------------|------------------------------------------------------------|

| 9:0     | 00 AM – 9:45 AM                                                                             |                                                            |

| 13<br>6 | Accurate Correlation Be<br>Measurement in High-sp<br>Designs<br>All Access Pass, 2-Day Pass | etween SI Simulation & peed Backplane Connector Ballroom G |

| 6<br>8  | DDR4-3200 FPGA-based<br>Power Aware SI Simulat<br>Correlation                               |                                                            |

|         | All Access Pass, 2-Day Pass                                                                 | Ballroom E                                                 |

| 1<br>13 | Generalized ccICN (Con<br>Integrated Crosstalk No                                           |                                                            |

|         | All Access Pass, 2-Day Pass                                                                 | Ballroom H                                                 |

| 8       | Integration-based Meth<br>Modeling of Copper Foi                                            | od for Surface Roughness<br>Is                             |

| •       | All Access Pass, 2-Day Pass                                                                 | Ballroom D                                                 |

| 7<br>13 | Optimal Design of High-<br>Interconnectors by App<br>Optimization & 3D Elect                | lying Bayesian<br>romagnetic Solvers                       |

|         | All Access Pass, 2-Day Pass                                                                 | Ballroom F                                                 |

| D       | Multi-Sensor Safety Cal<br>Applications                                                     | ibration for ADAS                                          |

|         | All Access Pass, 2-Day Pass                                                                 | Ballroom C                                                 |

#### **TRACKS AND LEGEND**

- () Signal & Power Integrity for Single-Multi Die, Interposer & Packaging

- (2) Chip I/O & Power Modeling

- Integrating Photonics & Wireless in Electrical Design

- Advances in Materials & Processing for PCBs, Modules & Packages 4

- Advanced I/O Interface Design for (5) Memory & 2.5D/3D/SiP Integrations

- 6 System Co-Design: Modeling, Simulation & Measurement Validation

- Optimizing High-Speed Link Design

- Measurement & Simulation Techniques for Analyzing Jitter, Noise & BER

- High-Speed Signal Processing, Equalization & Coding/FEC **(9**)

- Power Integrity in Power Distribution 10 Networks

- 1 Electromagnetic Compatibility & Interference

- 12 Applying Test & Measurement Methodology

- 13 Modeling & Analysis of Interconnects

- (14) Machine Learning for Microelectronics, Signaling & System Design

- Drive World Advanced Automotive

- (E) Embedded IoT World

- (8) Best Paper Awards Finalist

- 🛞 Boot Camp

- Chiphead Theater Presentation

- (iii) General Event

- ↔ Special Event

- Ø Sponsored Sessions

| 9:0     | 0 AM – 9:40 AM                                                                                                                    | 11           | :15 AM – 12:00 PM                                                                                                                    |                            |

|---------|-----------------------------------------------------------------------------------------------------------------------------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| Ø       | Developing High-Quality Test Fixtures for<br>De-embedding of S-ParametersOpen to AllGreat America Me                              |              | Improved Methodology to Accurately P<br>System Level Power Integrity Analysis<br>an ASIC Die<br>All Access Pass, 2-Day Pass          |                            |

| 10      | 00 AM – 11:00 AM                                                                                                                  |              | La suria a Osura a sala Misushama Dia A                                                                                              |                            |

| *<br>14 | Keynote – The Realities of Al & Machine         Cut Through the Hype & Move to Product         Open to All         Elizabeth A. H | ction (1)    | Learning Super-scale Microbump Pin A<br>Optimization for Real-world PCB Desig<br>Graph Representation<br>All Access Pass, 2-Day Pass |                            |

| 11      | 00 AM – 6:00 PM                                                                                                                   |              | Long-haul Inter-domain Power Noise                                                                                                   | •••••                      |

|         | Expo Hall Open<br>Open to All                                                                                                     | Expo Floor   | All Access Pass, 2-Day Pass                                                                                                          | Ballroom H                 |

| 11      | 00 AM – 11:10 AM                                                                                                                  | 6            | Performance Assessment of W-band Antennas of<br>Low-loss Inhomogeneous PCB Substrates                                                |                            |

| E       | Chairperson's Opening<br>Open to All                                                                                              | Ballroom B   | All Access Pass, 2-Day Pass                                                                                                          | Ballroom D                 |

| 11      | 10 AM – 11:40 AM                                                                                                                  | (2)          | Receiver Calibration & Testing Methode<br>Comparison for PAM-4 IOs                                                                   | ologies                    |

| E       | Towards Open-source Edge-cloud Colla<br>Architecture                                                                              | boration (8) | All Access Pass, 2-Day Pass                                                                                                          | Ballroom G                 |

|         | Open to All                                                                                                                       | Ballroom B   | Making Transit Modernization Accessit                                                                                                | ole: Lessons               |

| 11      | 10 AM – 11:50 AM                                                                                                                  |              | All Access Pass, 2-Day Pass                                                                                                          | Ballroom C                 |

| Ø       | Test compliance automation solution for<br>speed Ethernet interconnects using ZNr         Open to All       Great America Merica  | un 🕘         | Improving AR/VR Reality with 3D Time<br>Sensing<br>Open to All Chi                                                                   | of Flight<br>phead Theater |

#### **TRACKS AND LEGEND**

- () Signal & Power Integrity for Single-Multi Die, Interposer & Packaging

- 2 Chip I/O & Power Modeling

- Integrating Photonics & Wireless in Electrical Design

- Advances in Materials & Processing for PCBs, Modules & Packages

- Advanced I/O Interface Design for Memory & 2.5D/3D/SiP Integrations

- 6 System Co-Design: Modeling, Simulation & Measurement Validation

- Optimizing High-Speed Link Design

- B Measurement & Simulation Techniques for Analyzing Jitter, Noise & BER

- High-Speed Signal Processing, Equalization & Coding/FEC

- Power Integrity in Power Distribution Networks

- (1) Electromagnetic Compatibility & Interference

- Applying Test & Measurement Methodology

- 13 Modeling & Analysis of Interconnects

- Machine Learning for Microelectronics, Signaling & System Design

- Drive World Advanced Automotive

- Embedded IoT World

- Best Paper Awards Finalist

- 🛞 Boot Camp

- Chiphead Theater Presentation

- General Event

- 🛞 Special Event

- Ø Sponsored Sessions

#### 11:40 AM – 12:10 PM

| E        | App Startup Compiler Optimizations & Techniques<br>for Embedded Systems<br>Open to All Ballroom B                                        | 9           | Next Generation 224Gbps-PAM4 S<br>Channel & Link Systems<br>All Access Pass, 2-Day Pass | SERDES,<br>Ballroo       |

|----------|------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----------------------------------------------------------------------------------------|--------------------------|

| 12       | :10 PM – 12:40 PM                                                                                                                        | 8           | Noise Coupling Path Visualization                                                       | for Complex              |

| E        | The Great Chip Storage - ways to manage supply issues in IoT.         Open to All       Ballroom B                                       | (1)<br>(13) | Electronic Systems<br>All Access Pass, 2-Day Pass                                       | Ballroo                  |

| 12       | :10 PM – 12:50 PM                                                                                                                        | 2           | Parametric System Model of a 112<br>ADC-based SerDes for Architectu                     |                          |

| 0        | Power integrity measurement fundamentals           Open to All         Great America Meeting Room 2                                      | 7           | Validation Project Phases<br>All Access Pass, 2-Day Pass                                | Ballroo                  |

| 12       | :15 PM – 1:00 PM                                                                                                                         | 12          | :30 PM – 2:30 PM                                                                        |                          |

| 13<br>10 | A Comprehensive Study About Inhomogeneous<br>Dielectric Layers (IDLs) & the Impacts on Far-end<br>Crosstalk of High-speed PCB Striplines |             | Networking Session<br>Conference Networking Lunch<br>All Access Pass, 2-Day Pass        | Expo I                   |

|          | All Access Pass, 2-Day Pass Ballroom G                                                                                                   | 12:         | 40 PM – 1:20 PM                                                                         |                          |

| 8<br>12  | Challenges of Automated Stressed Receiver<br>Tolerance Testing: NRZ, PAM4 & Beyond<br>All Access Pass, 2-Day Pass Ballroom F             | E           | Panel – Processing Data at the Ed<br>Embedded Device<br>Open to All                     | lge with Your<br>Ballroo |

| D        | How A Standards-Based Framework Can Simplify                                                                                             | 1:1         | 5 PM – 2:00 PM                                                                          |                          |

|          | Camera & Display Integration in Automotive       Architectures       All Access Pass, 2-Day Pass       Ballroom C                        |             | Limits of High-speed Connector 8<br>Technology<br>Open to All                           | k Cable<br>Chiphead The  |

| •        | In Search of the Holy Grail: Laminate Dk & Df<br>Values that You Can Trust<br>Open to All Chiphead Theater                               |             |                                                                                         |                          |

|          | TRACKS A<br>To See Speakers for Each Session -                                                                                           |             |                                                                                         |                          |

- Signal & Power Integrity for Single-Multi Die, Interposer & Packaging

- (2) Chip I/O & Power Modeling

- Integrating Photonics & Wireless in Electrical Design

- Advances in Materials & Processing for (4) PCBs, Modules & Packages

- Advanced I/O Interface Design for (5) Memory & 2.5D/3D/SiP Integrations

- System Co-Design: Modeling, Simulation & Measurement Validation 6

- ⑦ Optimizing High-Speed Link Design

Measurement & Simulation Techniques for (8) Analyzing Jitter, Noise & BER

12:15 PM - 1:00 PM

- High-Speed Signal Processing, Equalization & Coding/FEC **(9**)

- Power Integrity in Power Distribution 10 Networks

- 1 Electromagnetic Compatibility & Interference

- Applying Test & Measurement Methodology

- Modeling & Analysis of Interconnects

- Machine Learning for Microelectronics, (14) Signaling & System Design

Drive World - Advanced Automotive

**Ballroom H**

**Ballroom E**

**Ballroom D**

**Expo Floor**

**Ballroom B**

Chiphead Theater

- Embedded IoT World

- (8) Best Paper Awards Finalist

- 🛞 Boot Camp

- Chiphead Theater Presentation

- General Event

- ↔ Special Event

- Ø Sponsored Sessions

ΗE В

| 1:2         | 20 PM – 2:35 PM                                                                                                            |                         | 2:                                     | 00 PM – 2:45 PM                                                                                            |                                       |       |

|-------------|----------------------------------------------------------------------------------------------------------------------------|-------------------------|----------------------------------------|------------------------------------------------------------------------------------------------------------|---------------------------------------|-------|

| E           | Sponsored Lunch Workshop Session: To<br>Devices Integration in Smart Homes<br>Open to All                                  | wards IoT<br>Ballroom B | D                                      | PCI Express Technology<br>Connectivity for the Nex<br>All Access Pass, 2-Day Pass                          |                                       |       |

| 2:0         | 00 PM – 2:40 PM                                                                                                            |                         | 2:                                     | 15 PM – 3:00 PM                                                                                            |                                       |       |

| Ø           | A comparison of solutions for jitter and r<br>separation                                                                   |                         | •                                      | New System-level Oppo<br>Open to All                                                                       | rtunities with OSFP-XI<br>Chiphead Th |       |

|             | Open to All Great America Mee                                                                                              | eting Room 2            | 2:                                     | 35 PM – 3:05 PM                                                                                            |                                       |       |

| 2:0         | 00 PM – 2:45 PM                                                                                                            |                         | E                                      | Lessons learned from b                                                                                     | uilding a connected                   |       |

| (1)<br>(12) | optical Modules                                                                                                            |                         |                                        | Open to All                                                                                                | /ML<br>Ballro                         | om B  |

|             | All Access Pass, 2-Day Pass                                                                                                | Ballroom E              | Automotive High-Speed Signal Protocols |                                                                                                            | Signal Protocols &                    |       |

| 8<br>3      | Impacts of Interferences & Crosstalk from<br>Adjacent Optical Channels on High-Performance<br>Silicon Photonic Transceiver |                         |                                        | Standards<br>Open to All                                                                                   | Mission City Ballroo                  | om B4 |

| 6           | All Access Pass, 2-Day Pass                                                                                                | Ballroom G              | 3:                                     | 00 PM – 3:45 PM                                                                                            |                                       |       |

| 4<br>13     | PCB Manufacturing Design Guidelines for<br>Reduction in Immersion Cooling<br>All Access Pass, 2-Day Pass                   | or Cost<br>Ballroom D   | (1)<br>(10)                            | A Comparison of Mothe<br>& Fully Integrated Voltag<br>Performance Optimized<br>All Access Pass, 2-Day Pass | ge Regulators for Powe                | er &  |

| 14<br>10    | Security Integrity Analytics by Thermal S<br>channel Simulation: An ML-augmented A<br>Approach                             |                         | 10<br>6                                | PDN Design Optimizatio<br>a Mixed-reality Display \$                                                       |                                       |       |

|             | All Access Pass, 2-Day Pass                                                                                                | Ballroom H              |                                        | All Access Pass, 2-Day Pass                                                                                | Ballro                                | E     |

| 8           |                                                                                                                            |                         | <b>(3)</b>                             | Proper Ground Return V<br>Signaling                                                                        | ia Placement for 40+ 0                | 3bps  |

| 12          |                                                                                                                            |                         | (13)                                   | All Access Pass, 2-Day Pass                                                                                | Ballro                                | oom F |

|             |                                                                                                                            |                         |                                        |                                                                                                            |                                       |       |

#### D

| To See Sp                                                                                                                                                                                                                | TRACKS AND LEGEND<br>eakers for Each Session – Download the DesignC                                                                             | on Event App                                                                                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| () Signal & Power Integrity for Single-Multi<br>Die, Interposer & Packaging                                                                                                                                              | Measurement & Simulation Techniques for<br>Analyzing Jitter, Noise & BER                                                                        | Drive Wo<br>E Embedd                                                                           |

| <ul> <li>2 Chip I/O &amp; Power Modeling</li> <li>3 Integrating Photonics &amp; Wireless in<br/>Electrical Design</li> <li>4 Advances in Materials &amp; Processing for</li> </ul>                                       | <ul> <li>High-Speed Signal Processing,<br/>Equalization &amp; Coding/FEC</li> <li>Power Integrity in Power Distribution<br/>Networks</li> </ul> | <ul> <li>Best Pap</li> <li>Boot Car</li> <li>Chiphead</li> </ul>                               |

| <ul> <li>Advances in Materials &amp; Processing for<br/>PCBs, Modules &amp; Packages</li> <li>Advanced I/O Interface Design for<br/>Memory &amp; 2.5D/3D/SiP Integrations</li> <li>System Co-Design: Modeling</li> </ul> | <ul> <li>(1) Electromagnetic Compatibility &amp;<br/>Interference</li> <li>(2) Applying Test &amp; Measurement<br/>Methodology</li> </ul>       | <ul> <li>(iii) General I</li> <li>(iii) Special E</li> <li>(iii) Ø</li> <li>(iii) Ø</li> </ul> |

| 6 System Co-Design: Modeling,<br>Simulation & Measurement Validation                                                                                                                                                     | Modeling & Analysis of Interconnects                                                                                                            |                                                                                                |

- 13 Modeling & Analysis of Interconnects

- (14) Machine Learning for Microelectronics, Signaling & System Design

- Drive World Advanced Automotive

- Embedded IoT World

- Best Paper Awards Finalist

- 🛞 Boot Camp

- Chiphead Theater Presentation

- General Event

- 🛞 Special Event

- Ø Sponsored Sessions

Optimizing High-Speed Link Design

| 3:0       | 00 PM – 3:45 PM                                                                                            |                        | 3:3               | 5 PM – 4:05 PM                                                                    |                                    |

|-----------|------------------------------------------------------------------------------------------------------------|------------------------|-------------------|-----------------------------------------------------------------------------------|------------------------------------|

| 12<br>(4) | Three Very Low-cost Technology Solution<br>Applications<br>All Access Pass, 2-Day Pass                     | s for SI<br>Ballroom H | E                 | How to Select the Best RTOS<br>Device<br>Open to All                              | 6 for your Connected<br>Ballroom B |

| 6         | Validation Shift-left: Enabling Early SerDes Mixed-                                                        |                        | 4:00 PM – 4:40 PM |                                                                                   |                                    |

| 7         | signal Validation<br>All Access Pass, 2-Day Pass                                                           | Ballroom G             | Ø                 | Automotive Ethernet MGBase testing                                                | e-T Compliance                     |

| D         | Building Safe & Secure Systems Using Open<br>Source                                                        |                        |                   |                                                                                   | at America Meeting Room 2          |

|           |                                                                                                            | Ballroom C             | 4:0<br>(14)       | 0 PM – 5:15 PM<br>Panel – AI & Digital Twins for                                  | SI/PI Analysis &                   |

| 3:0       | 00 PM – 3:40 PM                                                                                            |                        | $\check{2}$       | Design<br>Open to All                                                             | Ballroom G                         |

| Ø         | Practical signal integrity measurements of<br>embedded serial interfaces<br>Open to All Great America Meet |                        | 10<br>12          | Panel – Modeling Passive Co<br>Integrity Simulations: How to<br>Model, How to Use | mponent for Power                  |

| 3:0       | 05 PM – 3:35 PM                                                                                            |                        |                   | Open to All                                                                       | Ballroom H                         |

| E         | Augmented-Reality Optical Narrowcasting<br>Open to All                                                     | g (ARON)<br>Ballroom B | 9                 | Panel – OIF Electrical I/O Spe<br>on CEI 112Gbps & 224Gbps                        | ecifications: Progress             |

| 3:1       | 5 PM – 4:00 PM                                                                                             |                        | 0                 | Open to All                                                                       | Ballroom D                         |

| ()<br>()  | Bespoke Silicon: How Systems Companie<br>Driving Chip Design<br>Open to All Chiphe                         | es are<br>ead Theater  | D                 | Panel – Implementing a Digit<br>Framework for Automotive A<br>Open to All         |                                    |

#### **TRACKS AND LEGEND**

- () Signal & Power Integrity for Single-Multi Die, Interposer & Packaging

- 2 Chip I/O & Power Modeling

- Integrating Photonics & Wireless in Electrical Design

- Advances in Materials & Processing for PCBs, Modules & Packages

- Advanced I/O Interface Design for Memory & 2.5D/3D/SiP Integrations

- 6 System Co-Design: Modeling, Simulation & Measurement Validation

- Optimizing High-Speed Link Design

- B Measurement & Simulation Techniques for Analyzing Jitter, Noise & BER

- High-Speed Signal Processing, Equalization & Coding/FEC

- Power Integrity in Power Distribution Networks

- (1) Electromagnetic Compatibility & Interference

- Applying Test & Measurement Methodology

- 13 Modeling & Analysis of Interconnects

- Machine Learning for Microelectronics, Signaling & System Design

- Drive World Advanced Automotive

- Embedded IoT World

- Best Paper Awards Finalist

- 응 Boot Camp

- Chiphead Theater Presentation

- General Event

- 🛞 Special Event

- Ø Sponsored Sessions

# WHERE THE CHIP MEETS THE BOARD

# **SESSIONS – WEDNESDAY, APRIL 6**

#### 4:15 PM - 5:00 PM

Production ML for Mission-Critical Applications

Open to All

Chiphead Theater

#### 5:00 PM - 6:00 PM

Networking Session Booth Bar Crawl Open to All

**Expo Floor**

Sponsored by:

CARLISLE

### **Tektronix**<sup>®</sup>

Amphenol

#### TRACKS AND LEGEND

- () Signal & Power Integrity for Single-Multi Die, Interposer & Packaging

- Chip I/O & Power Modeling

- Integrating Photonics & Wireless in Electrical Design

- Advances in Materials & Processing for PCBs, Modules & Packages

- Advanced I/O Interface Design for Memory & 2.5D/3D/SiP Integrations

- 6 System Co-Design: Modeling, Simulation & Measurement Validation

- Optimizing High-Speed Link Design

- Measurement & Simulation Techniques for Analyzing Jitter, Noise & BER

- High-Speed Signal Processing, Equalization & Coding/FEC

- Power Integrity in Power Distribution Networks

- (1) Electromagnetic Compatibility & Interference

- Applying Test & Measurement Methodology

- Modeling & Analysis of Interconnects

- Machine Learning for Microelectronics, Signaling & System Design

- Drive World Advanced Automotive

- Embedded IoT World

- Best Paper Awards Finalist

- 🛞 Boot Camp

- Chiphead Theater Presentation

- General Event

- 🛞 Special Event

- Sponsored Sessions

### cādence<sup>®</sup>

# **Unleash Imagination**

#### Turn Great Ideas into Reality

- System design and analysis tools

- Silicon-proven IP

- Advanced IC packaging

- Photonics design automation

#### Visit Us in Booth 927

#### www.signalintegrityjournal.com

#### **FREE** subscription gets you:

- **EMC/EMI, Signal Integrity, and Power Integrity topics**

- In-depth, Peer-Reviewed Technical Articles

- Insights from Industry Leaders

- Product & Industry News

- Webinars & Podcasts

- White Papers

- Print editions/technical e-books

#### 8:00 AM - 8:45 AM

| 7<br>6        | <b>112G-PAM4-QSFP Interconnect: A</b><br><b>Cooling &amp; Immersion Cooling</b><br>All Access Pass, 2-Day Pass                                    | Study in Air<br>Ballroom F |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| 12<br>9       | Equalizer (Tx/Rx) Optimization at 1<br>All Access Pass, 2-Day Pass                                                                                | 12Gbps<br>Ballroom H       |

| 8<br>14<br>10 | Imitate Expert Policy & Learn Beyon<br>PDN Optimizer by Imitation Learnin<br>All Access Pass, 2-Day Pass                                          |                            |

| 1             | Imitation Learning with Bayesian Ex<br>(IL-BE) for Signal Integrity (SI) of PA<br>High-speed Serial Link: PCIe 6.0<br>All Access Pass, 2-Day Pass | -                          |

| (4)<br>(7)    | PCB Stackup & Launch Optimization<br>speed PCB Designs<br>All Access Pass, 2-Day Pass                                                             | on in High-<br>Ballroom E  |

| D             | Open Standard Acceleration APIs for<br>Critical Graphics, Vision & Compute<br>All Access Pass, 2-Day Pass                                         | -                          |

#### 9:00 AM - 9:45 AM

| 9<br>(7)   | How to Optimize TxFFE &<br>From the Optimization                                                                | What We Can Learn                            |

|------------|-----------------------------------------------------------------------------------------------------------------|----------------------------------------------|

|            | All Access Pass, 2-Day Pass                                                                                     | Ballroom E                                   |

| (1)<br>(6) | Magnetic Near-field Evalu<br>for Integrated Circuit In-p<br>Assessment                                          | ackage Coupling                              |

|            | All Access Pass, 2-Day Pass                                                                                     | Ballroom D                                   |

| <b>1</b> 0 | New Power Integrity Meth<br>Effect of PDN Voltage Dee                                                           |                                              |

| U          | All Access Pass, 2-Day Pass                                                                                     | Ballroom G                                   |

| 13<br>12   | Understanding S Parame<br>& the Application to Two X<br>Removal of High-speed In<br>All Access Pass, 2-Day Pass | X Automatic Fixture                          |

|            | All Access 1 ass, 2-Day 1 ass                                                                                   | Dailooniii                                   |

| 4          | Understanding the Effect<br>Permittivity & Loss of Die                                                          |                                              |

|            | All Access Pass, 2-Day Pass                                                                                     | Ballroom H                                   |

| D          | Enhancing Safety & Perfo<br>a Motion First Approach t                                                           |                                              |

|            | All Access Pass, 2-Day Pass                                                                                     | Ballroom C                                   |

| 0          | No Exit Ramps Needed-C<br>Workflow Delivers Seamle<br>Reducing Turnaround Tim<br>Risk                           | ess In-Design Analysis,<br>ne and Minimizing |

|            | Open to All                                                                                                     | Mission City Ballroom B5                     |

#### TRACKS AND LEGEND

- () Signal & Power Integrity for Single-Multi Die, Interposer & Packaging

- (2) Chip I/O & Power Modeling

- Integrating Photonics & Wireless in Electrical Design

- Advances in Materials & Processing for PCBs, Modules & Packages

- Advanced I/O Interface Design for Memory & 2.5D/3D/SiP Integrations

- 6 System Co-Design: Modeling, Simulation & Measurement Validation

- Optimizing High-Speed Link Design

- B Measurement & Simulation Techniques for Analyzing Jitter, Noise & BER

- High-Speed Signal Processing, Equalization & Coding/FEC

- Power Integrity in Power Distribution Networks

- (1) Electromagnetic Compatibility & Interference

- Applying Test & Measurement Methodology

- 13 Modeling & Analysis of Interconnects

- Machine Learning for Microelectronics, Signaling & System Design

- Drive World Advanced Automotive

- Embedded IoT World

- Best Paper Awards Finalist

- 🛞 Boot Camp

- Chiphead Theater Presentation

- General Event

- 🛞 Special Event

- Ø Sponsored Sessions

| 10 | 100  AW = 1100  AW                                                                                                |                                            |

|----|-------------------------------------------------------------------------------------------------------------------|--------------------------------------------|

| •  | Keynote – Space Tech: Pres<br>Open to All                                                                         | ent & Future<br>Elizabeth A. Hangs Theater |

| 11 | :00 AM – 6:00 PM                                                                                                  |                                            |

|    | Expo Hall Open<br>Open to All                                                                                     | Expo Floor                                 |

| 11 | :00 AM – 11:25 AM                                                                                                 |                                            |

| E  | Chairperson's Opening - Se<br>Update                                                                              | miconductor                                |

|    | Open to All                                                                                                       | Ballroom B                                 |

| 11 | :00 AM – 11:45 AM                                                                                                 |                                            |

| Ø  | Overview and Challenges of<br>Interposers                                                                         | f Running D2D over                         |

|    | Open to All                                                                                                       | Mission City Ballroom B5                   |

| 11 | :15 AM – 12:00 PM                                                                                                 |                                            |

| 2  | COM-based IBIS-AMI for 10<br>Compliance                                                                           | 6/112Gbps System                           |

|    | All Access Pass, 2-Day Pass                                                                                       | Ballroom D                                 |

| 14 | Data-Efficient Machine Lean<br>Hardware Routing: Signal In<br>to 2PDC and PCIe 6.0<br>All Access Pass, 2-Day Pass |                                            |

|    | MI AUUESS FASS, 2-Day Fass                                                                                        | Daiirooni E                                |

Practical Methods of Estimating Dynamic Current

#### 11:15 AM - 12:00 PM

| 1  | (1) Thermal Transmission Line: Smoothing Thermal<br>Gradients & Lowering Temperature for Signal<br>Integrity Improvement of HBM & 2.5D ICs |                      |  |

|----|--------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--|

|    | All Access Pass, 2-Day Pass                                                                                                                | Ballroom F           |  |

| 8  | Transmitter Jitter Measuremer<br>PAM-4 IOs                                                                                                 | nt Methodologies for |  |

|    | All Access Pass, 2-Day Pass                                                                                                                | Ballroom G           |  |

| D  | Moving Towards High Resolut<br>Radar Systems                                                                                               | ion Automotive       |  |

|    | All Access Pass, 2-Day Pass                                                                                                                | Ballroom C           |  |

|    | Five Tips for Power Integrity N<br>Budget                                                                                                  | leasurements on a    |  |

|    | Open to All                                                                                                                                | Chiphead Theater     |  |

| 11 | :25 AM – 11:55 AM                                                                                                                          |                      |  |

| E  | Smoke and Mirrors: community world                                                                                                         | cation in the IoT    |  |

|    | Open to All                                                                                                                                | Ballroom B           |  |

| 11 | :55 AM – 12:25 PM                                                                                                                          |                      |  |

| E  | It's just a Vulnerable Compute<br>Autonomous Systems                                                                                       | r: Protecting        |  |

|    | Open to All                                                                                                                                | Ballroom B           |  |

### **TRACKS AND LEGEND**

#### To See Speakers for Each Session – Download the DesignCon Event App

Signal & Power Integrity for Single-Multi Die, Interposer & Packaging

for Calculating PDN Target Z

(2) Chip I/O & Power Modeling

All Access Pass, 2-Day Pass

- Integrating Photonics & Wireless in Electrical Design

- Advances in Materials & Processing for PCBs, Modules & Packages 4

- Advanced I/O Interface Design for (5) Memory & 2.5D/3D/SiP Integrations

- 6 System Co-Design: Modeling, Simulation & Measurement Validation

- Optimizing High-Speed Link Design

- Measurement & Simulation Techniques for Analyzing Jitter, Noise & BER (8)

- High-Speed Signal Processing, Equalization & Coding/FEC **(9**)

**Ballroom H**

- Power Integrity in Power Distribution 10 Networks

- 1 Electromagnetic Compatibility & Interference

- 12 Applying Test & Measurement Methodology

- Modeling & Analysis of Interconnects

- (14) Machine Learning for Microelectronics, Signaling & System Design

- Drive World Advanced Automotive

- (E) Embedded IoT World

- (8) Best Paper Awards Finalist

- 🛞 Boot Camp

- Chiphead Theater Presentation

- General Event

- ↔ Special Event

- Ø Sponsored Sessions

(2)

#### 12:00 PM - 2:45 PM 12:15 PM - 1:00 PM Addressing 112G Connector+PCB Modeling Transient vs. Statistical: A Comparative (8) Without Having to Simulate with Terabyte **Study on Practical Parallel Link Qualification** Servers Techniques Open to All **Mission City Ballroom B5** All Access Pass, 2-Day Pass **Ballroom H** 12:25 PM - 12:35 PM 12:15 PM - 12:25 PM A Study on 224G Channel Characteristics De-embedding Method for 224G High Bandwidth **Chiphead Theater Chiphead Theater** 6) Open to All (12) Open to All 12:15 PM - 1:00 PM 12:25 PM - 12:55 PM Automotive Semis Shifts into Overdrive Symmetrical Multi-Processing (SMP) with All Access Pass, 2-Day Pass FreeRTOS and Raspberry Pi Pico **Ballroom** C Open to All **Ballroom B** 3 Electro-optic & Custom Photonic Co-design in 12:30 PM - 2:30 PM Monolithic Silicon Photonics Technology All Access Pass, 2-Day Pass **Ballroom E Networking Session** (圖) **Conference Networking Lunch** Investigation of Low-etch or Non-oxide Surface All Access Pass, 2-Day Pass **Expo Floor** Treatment on Stripline Insertion Loss All Access Pass, 2-Day Pass **Ballroom G** 12:35 PM - 12:45 PM **Optimal PDN Design Method for Mobile Phone Reflecting on Reflections: An Evaluation of New &** Based on Q-learning Algorithm with Dynamic PI **Standardized Metrics** (10) Simulation All Access Pass, 2-Day Pass Ballroom D Open to All **Chiphead Theater** 6 System Co-design for Sleek Detachable/tablet 12:55 PM - 1:35 PM **Reference Design Equipment Teardown Session by Omdia** All Access Pass, 2-Day Pass **Ballroom F** Open to All Ballroom B

#### TRACKS AND LEGEND

- Signal & Power Integrity for Single-Multi Die, Interposer & Packaging

- Chip I/O & Power Modeling

- Integrating Photonics & Wireless in Electrical Design

- Advances in Materials & Processing for PCBs, Modules & Packages

- Advanced I/O Interface Design for Memory & 2.5D/3D/SiP Integrations

- System Co-Design: Modeling, Simulation & Measurement Validation

- Optimizing High-Speed Link Design

- Measurement & Simulation Techniques for Analyzing Jitter, Noise & BER

- High-Speed Signal Processing, Equalization & Coding/FEC

- Power Integrity in Power Distribution Networks

- (1) Electromagnetic Compatibility & Interference

- Applying Test & Measurement Methodology

- 13 Modeling & Analysis of Interconnects

- Machine Learning for Microelectronics, Signaling & System Design

- Drive World Advanced Automotive

- Embedded IoT World

- Best Paper Awards Finalist

- 응 Boot Camp

- Chiphead Theater Presentation

- General Event

- 🛞 Special Event

- Ø Sponsored Sessions

#### 1:00 PM - 1:45 PM

**MIPI C-PHY System Design Exploration and Optimization for Signal Integrity Analysis by Using** Advanced Cadence Compliance Kit Open to All **Mission City Ballroom B5** 1:15 PM - 2:00 PM 400/800GbE Interconnects: The Challenges & **Resolutions for Cabling Complexity, Serviceability** (7) & Rack Power Open to All **Chiphead Theater** 2:00 PM - 2:45 PM 224Gbps-PAM4 End-to-end Channel Solutions for **High-density Networking System**  $\overline{\mathbf{7}}$ All Access Pass, 2-Day Pass **Ballroom H** (6) Applications of High Bandwidth AWGs in Receiver Testing: Tricks of the Trade (12) All Access Pass, 2-Day Pass Ballroom E (7) Current Limitation & New Method to Accurately Estimate Reference Signal Jitter for 100+ Gbps (8) 802.3 & OIF/CEI Interference Tolerance Test

All Access Pass, 2-Day Pass

#### 2:00 PM - 2:45 PM

Open to All

Effective Intra-pair Skew, EIPS & Intra-pair Skew (13) Modeling Method (1) All Access Pass, 2-Day Pass **Ballroom G** (10) Novel Power-integrity Solutions for Multi-HSIO with Silicon Co-relation (6) All Access Pass, 2-Day Pass **Ballroom F Measurements & Test of High Speed Serial Buses: Measurement Bandwidth in Ethernet for** Automotive, Electrical & Optical All Access Pass, 2-Day Pass **Ballroom C** Mainstream Signal Integrity Workflow for PCIe 6.0 PAM4 Signaling Open to All **Mission City Ballroom B5** 2:15 PM - 3:00 PM The Next Tipping Point for Semiconductors Open to All **Chiphead Theater** 2:35 PM - 3:05 PM Providing the Best Industrial IoT Gateway

**Platforms for Device Connectivity & Management**

#### **TRACKS AND LEGEND**

#### To See Speakers for Each Session – Download the DesignCon Event App

- Signal & Power Integrity for Single-Multi Die, Interposer & Packaging

- 2 Chip I/O & Power Modeling

- Integrating Photonics & Wireless in Electrical Design

- Advances in Materials & Processing for PCBs, Modules & Packages

- Advanced I/O Interface Design for Memory & 2.5D/3D/SiP Integrations

- System Co-Design: Modeling, Simulation & Measurement Validation

- Optimizing High-Speed Link Design

- Measurement & Simulation Techniques for Analyzing Jitter, Noise & BER

- High-Speed Signal Processing, Equalization & Coding/FEC

**Ballroom D**

- Power Integrity in Power Distribution Networks

- (f) Electromagnetic Compatibility & Interference

- Applying Test & Measurement Methodology

- 13 Modeling & Analysis of Interconnects

- Machine Learning for Microelectronics, Signaling & System Design

Drive World — Advanced Automotive

**Ballroom B**

- Embedded IoT World

- (8) Best Paper Awards Finalist

- 🛞 Boot Camp

- Chiphead Theater Presentation

- General Event

- 🛞 Special Event

- Ø Sponsored Sessions

#### 3:00 PM - 3:45 PM

| 5<br>6                | erface<br>ning                                                                                 |             |

|-----------------------|------------------------------------------------------------------------------------------------|-------------|

|                       | <b>Technique</b><br>All Access Pass, 2-Day Pass                                                | Ballroom E  |

| 8<br>(4)              | Experiment & Simulation Studies on Re<br>due to Period Structure in PCBs                       | esonances   |

| 13                    | All Access Pass, 2-Day Pass                                                                    | Ballroom D  |

| (7)<br>(12)           | Exploring the Requirements for 224Gbp<br>Channel Characterization Using Simula<br>Measurements |             |

|                       | All Access Pass, 2-Day Pass                                                                    | Ballroom F  |

| 8<br>(2)              | IBIS-AMI Modeling & Correlation Metho<br>ADC-Based SerDes Beyond 100Gbps                       | odology for |

| $\check{\mathcal{O}}$ | All Access Pass, 2-Day Pass                                                                    | Ballroom G  |

| 8<br>6                | Optimization of a Co-packaged Laser N<br>Design Using Statistical Analysis for Si<br>Integrity |             |

| $(\mathbf{I})$        | All Access Pass, 2-Day Pass                                                                    | Ballroom H  |

| D                     | Role of Open Standards for the Long-te<br>Sustainability of Networking Technolog               |             |

|                       | All Access Pass, 2-Day Pass                                                                    | Ballroom C  |

| $\sim$                |                                                                                                |             |

(@) The Future of 224G Serial Links Open to All **Mission City Ballroom B5**

#### 3:05 PM - 3:35 PM